Building on the success of its predecessors, the fourth Photonic Integrated Circuits (PIC) International Conference (26-27 March) pinpointed the most promising opportunities accross industry. More than 700 attended the co-located conferences that focused on advances in PICs, compound semiconductors and the future of advanced sensor solutions.

As conference Co-Chairs Dr. Michael Lebby and Dr. Bill Ring note in their wrap-up article, the PIC International Conference continues to exceed expectations. Hundreds of attendees filled meeting spaces. As photonic integration and silicon photonics (SiP) technologies continue to mature, interest in the technology also grows. PICs are seeing wider adoption while more research efforts into hybridization and new materials are expanding what PICs can do in wider markets.

If you were unable to join us in Brussels, be sure to read the event summary article from our conference chairpersons. Some of the best in our industry were honored with 2019 PIC Awards – see their profiles in a separate article. Two notable PIC honorees are Dr. Graham Reed, a professor at the University of Southampton and leading pioneer in silicon photonics (SiP). We have an in-depth look at Reed’s CORNERSTONE programme and its growing MPW and training programs. Also honored was Dr. Martin Schell, the Executive Director of Fraunhofer HHI (Berlin) and Chair of Optic and Optoelectronic Integration at the Technical University of Berlin. He is a regular contributor to PIC magazine; we have included one of his articles that details some of the Institute’s latest advances.

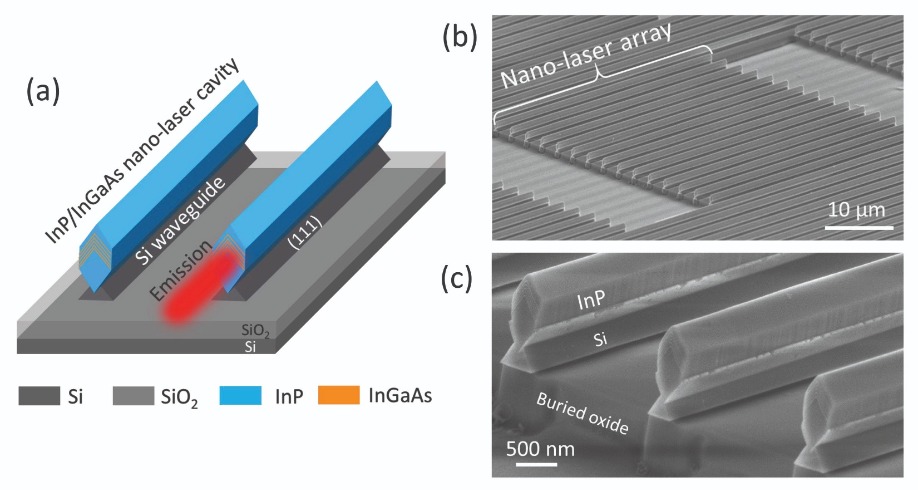

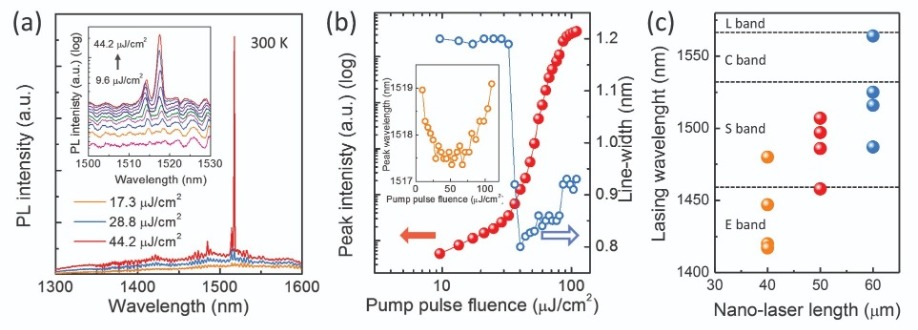

Also in this PIC Magazine is a look at work being done at the Hong Kong University of Science and Technology to grow InP-based lasers on precisely oriented silicon. If this research proves manufacturable it could help remove one of the barriers to more seamless monolithic integration. In a different look at lasers for silicon photonics we have an article from the Samsung Advanced Institute of Technology describing new SiP lasers that do not require insulating intermediary layers.

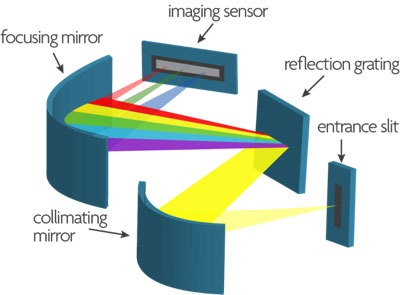

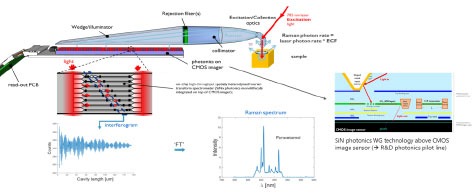

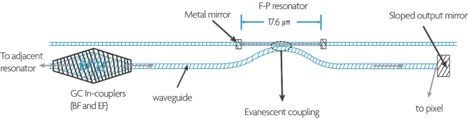

We also have an article from imec (Belgium) discussing a unique approach using SiP micro mirrors to miniaturize the high-caliber performance of Raman spectroscopy desktop-size instruments for the development of new handheld Raman spectroscopes. While we can’t say whether a Raman spectroscope might be an option for future smartphones, imec’s researchers are proving that integrated photonics and silicon photonics are just beginning to show their capabilities across wider swaths of photonics applications.

We hope you enjoy this edition of PIC Magazine and look forward to seeing you at PIC International 2020 in Brussels.

ficonTEC Service GmbH and Coherent Solutions, New Zealand, have entered into a collaborative partnership to advance electro-optical measurement capability for use in volume testing within the manufacturing cycle of integrated photonic devices (PICs).

As optical and electrical technologies become more miniaturized, complex, and increasingly integrated with one another’s underlying architecture, the more inefficient and frustrating it is for process engineers to implement separate electrical and optical test and qualification procedures. To avoid this, engineers require fully-automated systems that can perform complex precision alignment and assembly, as well as combined electro-optical I/O measurements for complex integrated photonic devices – from singulated dies, through to wafer-level and even up to fully-packaged devices.

According to Ignazio Piacentini, Business Development Director at ficonTEC, “Wafer-level testing of PICs differs substantially from that of conventional semiconductor wafers and requires the integration of three major ingredients: Firstly, high-accuracy, sub–µm optical positioning with fast-active alignment capabilities. Secondly, some form of combined electro-optical probe head, and thirdly, modular high-channel-count instrumentation. ficonTEC and Coherent Solutions already provide the necessary capabilities for the first and last ingredients, and together we are actively researching electrical/optical probe head concepts.”

Coherent Solutions’ broad portfolio of photonic test and measurement instruments includes a line-up of modules for the popular PXI platform that leverage National Instruments’ established LabVIEW graphical programming environment. As ficonTEC’s PCM (ProcessControlMaster) software is also based around LabVIEW, integration of the two is seamless and enables the creation of sophisticated and fully-automated test solutions to match individual requirements.

Alternatively, to achieve the same goal within non-LabVIEW and alternative instrumentation environments, Coherent Solutions additionally offers the same optical measurement capability in a range of compact, modular benchtop and IOT-focused test equipment that can be equally well interfaced to ficonTEC’s process control software. Either approach can be flexibly used by manufacturers to speed up development and production of the latest photonic integrated circuits and devices.

Andy Stevens, CEO of Coherent Solutions says, “The last 20 years of investment into technology for optical communications is now spawning new capabilities and products in new applications and markets, which in turn encourages further development and innovation. We are fortunate to support this innovation and are incredibly excited to work with ficonTEC on new automated test and measurement solutions for manufacturers. Our complementary product platforms and design philosophies enable rapid customization and deployment and provide a clear upgrade path as technology advances and products evolve. For customers, this increases ROI and helps them bring new products to market faster and cheaper. Together, we will provide customers with unique products and unrivalled value and support.”

Torsten Vahrenkamp, CEO of ficonTEC Service added, “The collaboration with Coherent Solutions could not come at a better time, as a number of our current activities are geared to further improving performance and capability for our new, next-generation assembly and test systems. By integrating Coherent Solutions’ innovative optical instrumentation and software into our modular machine architecture and process control software, respectively, we take a significant step forward in our continued and growing support for integrated photonics developments worldwide.”

The two companies are initially focusing their sights on manufacturers of modules and components for telecom and datacom, and on systems for testing high-density VCSEL systems as used in 3D optical sensing/imaging applications, such as for automotive LIDAR and for face recognition modules found in smartphones.

ficonTEC and Coherent Solutions will display the initial results of this collaboration with a live demonstration of a fully-automated photonics test system at NIWeek in Austin, TX/USA, from May 20-23, and again at Laser World of Photonics in Munich, Germany, from June 24-27, 2019.

Researchers at Cardiff University have shown tiny light-emitting nanolasers less than a tenth of the size of the width of a human hair can be integrated into silicon chip design.

The photonic band-edge lasers can operate at superfast speeds and have the potential to help the global electronics industry deliver a range of new applications – from optical computing to remote sensing and heat seeking,

“This is the first demonstration that shows how photonic band-edge lasers can be integrated directly on patterned silicon-on-insulator platforms,” said Diana Huffaker scientific director of Cardiff University’s Institute for Compound Semiconductors (ICS). Huffake specialises in nanoscale epitaxy, fabrication and optoelectronic devices.

“Silicon is the most widely used material in semiconductor industries. However, it has been difficult to integrate compact light sources on this material. Our research breaks through this barrier by developing extremely small lasers integrated on silicon platforms, applicable to various silicon-based electronic, optoelectronic, and photonic platforms.”

The paper, 'Room‐Temperature InGaAs Nanowire Array Band‐Edge Lasers on Patterned Silicon‐on‐Insulator Platforms', has been published in Physica Status Solidi - RRL.

Wyn Meredith, director of the Compound Semiconductor Centre, a Joint Venture between IQE Plc and Cardiff University, said: “This research will have long-term implications in the rapidly expanding field of photonics, with a particular emphasis on driving commoditisation of high volume, high specification optical components for mass market communications and sensing applications.“

Cardiff University, IQE and the Compound Semiconductor Centre are members of CS Connected – the world’s first hub for compound Semiconductor technologies based in South Wales.

The ICS is due to move to a new state-of-the-art Translational Research Facility on Cardiff Innovation Campus in 2021.

The Ferdinand-Braun-Institut, Leibniz-Institut für Höchstfrequenztechnik (FBH) is showing its range of services at Laser World of Photonics in Munich from June 24-27, 2019. At the joint Berlin-Brandenburg stand, the institute will present current developments, from chips and modules with and without fibre coupling to live demonstrators. At the accompanying CLEO conference, FBH will be represented with 16 scientific contributions.

LiDAR demonstrator: stand-alone, PC-controlled pulsed laser source

As part of 'Research Fab Microelectronics Germany', FBH is presenting a live demonstrator for pulsed laser sources, which allows flexible adjustment of pulse duration and intensity. Visitors can use a tablet to change the desired parameters and monitor the results in real time on screen.

With its PLS flex, FBH offers laser sources that deliver pulses in the range from 200 ps to 20 ns. The systems can be equipped with diode lasers of various wavelengths (630 - 1180 nm) and power ranges. Laser diodes, which are wavelength stabilised at 905 nm, achieve output powers of up to 100 W at ambient temperatures of up to 85degC. This makes them suited for use in LiDAR systems. FBH offers the chips in a complete development environment with driver electronics and control software.

The compact turnkey laser system for Raman measurements is equipped with a monolithic Y-dual-wavelength diode laser, which alternately emits light at two slightly different wavelengths. The system allows very fast measurements using Shifted Excitation Raman Difference Spectroscopy (SERDS). The spectral distance of both wavelengths can be adjusted via micro heaters above the DBR gratings, which define the wavelength. If the systems are complemented with a suitable power supply, spectrometer, data acquisition and software interface, they can be used for on-site measurements. In-house developed, portable systems have already been successfully used for measurements on food, soil, plants and human skin.

In a recent paper in Phys. Status Solidi A, Chinese researchers have demonstrated light emission from a silicon p‐channel MOSFET with a 6μm effective gate length that is operated as a three‐terminal gate‐controlled LED.

Using a photon‐emission microscope with a detector responsive to the range of 200–1000 nm, they measured emission spectra in the range of 400 to 900 nm which includes visible light radiation.

The team, led by Kaikai Xu at the State Key Laboratory of Electronic Thin Films and Integrated Devices in the University of Electronic Science and Technology of China, say the fabrication of the device is fully compatible with CMOS processing procedures.

Since the MOS‐like diode uses the field effect induced by the gate for modulation of the diode's space charge electric field (and hence the optical output from the LED), the modulation speed for visible and infrared bands can attain high frequencies in the GHz range.

Such high frequencies represent a significant leap in silicon electro-optic modulator performance for future optoelectronic interconnects using standard CMOS processes.

The lifetime of the MOS-capacitor LED should be controllable via the capacitor discharge time. In other words, the Si gate-controlled diode LED operates on the principle of the MOS-capacitor and not on standard p-n junctions. In contrast to the lifetime of carriers in the depletion region, the MOS-capacitor discharge time also determines the modulation in the reverse-bias silicon p-n junction with gate control.

Light generation from a Si‐LED provides a way to manufacture all‐silicon monolithically integrated optoelectronic systems composed of CMOS transistors and Si‐LEDs fabricated on the same chip.

'Silicon MOS Optoelectronic Micro‐Nano Structure Based on Reverse‐Biased PN Junction' by Kaikai Xu; Phys. Status Solidi A March 2019 https://doi.org/10.1002/pssa.201800868

Lumerical, a developer of photonic design and simulation tools and Luceda Photonics, developer of IPKISS, a reference platform for Integrated Photonic design and photonic PDKs have announced the immediate availability of a new photonic flow that integrates Lumerical’s FDTD Solutions photonic simulator and Luceda’s IPKISS. These products, familiar to photonic component designers, create a complete flow linking Lumerical and Luceda’s powerful PIC design frameworks, providing designers with the choice to use their favored tools at each stage in their design flow.

Responding to multiple customer requests, Luceda Photonics and Lumerical are committed to integrated photonics designers and developed a link between IPKISS and Lumerical FDTD solutions. The link enables component designers to combine IPKISS PCells with simulation recipes to ensure that components are simulated in Lumerical FDTD Solutions using validated methods on 3D structures that match the fabricated device. Both IPKISS PCells and the simulation recipes are written in Python enabling designer control of the PCell and the associated simulation methodology. The designer can ensure consistency between layout, fabrication process and the generated simulation results that can be further used in the IPKISS and Lumerical design solutions.

Prof. Wim Bogaerts said “At Ghent University we have been interfacing IPKISS and Lumerical for several years now and we are enthusiastically using it for both research and teaching. We are very happy to learn that there will be an official link between IPKISS and Lumerical, and we’re looking forward to enjoy the benefits of this collaboration”.

Erwin De Baetselier, Luceda CEO said “We are really excited about our new collaboration with Lumerical. We are particularly thrilled about using Lumerical’s Python API. IPKISS fully embraces the Python ecosystem and through this new link Lumerical and Luceda Photonics provide the first complete design platform that is completely scriptable from Python.”

James Pond, Lumerical Founder & CTO remarked, “Integration with Luceda is a consistent request from many photonic component design customers. This integration with Luceda, a leader in Python-based mask layout of photonic designs, expands the ecosystem for designers using familiar tools, and further demonstrates our commitment to the Python community.”

Infinera and Fastweb, a major Italian telecoms operator, have announced the successful demonstration of 500 gigabits per second (500G) single-wavelength service connectivity in a production network using Infinera’s configurable technology on the Groove platform. The high-speed optical transmission demonstration, the first in Italy, spanned over 180km on Fastweb’s low-latency long-haul backbone network, between Milan and Turin.

Conducted over Fastweb’s live fibre route between Milan and Turin, the 500G single-wavelength trial demonstrated Fastweb’s capability to easily and efficiently scale its infrastructure network to meet the increasing bandwidth demands of its end-user customers. The trial was implemented over Fastweb’s existing optical infrastructure without special amplifiers, tuning, or changes.

“Providing our customers with resilient, high-quality, and innovative solutions is in Fastweb’s DNA,” said Andrea Lasagna, CTO, Fastweb. “As the market for high-performance long-haul transport continues to grow at an accelerated pace, a scalable and simple network approach is required to satisfy the growing demand for bandwidth. This trial confirms the outstanding performance provided by Infinera’s innovative solution, which enables us to deliver a best-in-class customer experience at the highest transmission speeds.”

Infinera’s 7300 Multi-Haul Transport Platform, mTera Universal Switching Platform and Groove 600G technology are part of Fastweb’s backbone network spanning over 650 nodes and providing the flexibility and future development and delivery of a range of programmable high-speed end-user services at 400G, 500G, and up to 600G. Infinera’s solution enables Fastweb to scale internet exchange point capacity up to 24 terabits per second, while offering ease of deployment and network investment efficiency.

“We are pleased to extend our technology partnership with Fastweb to bring the benefits of cutting-edge coherent optical transmission to their customers,” said Glenn Laxdal, senior VP, product line management, Infinera. “Our ability to introduce higher-speed transmission over existing infrastructures is a key part of our mission to help our customers to effectively meet their increasing bandwidth needs.”

Infinera has announced that Cyxtera Technologies, a secure infrastructure company, has deployed the Infinera Groove Network Disaggregation Platform to support delivery of secure and reliable high-speed data centre interconnect services.

The Infinera Groove solution enables Cyxtera to cost-efficiently scale optical interconnect capacity between its data centre facilities within major markets while meeting the business-critical, low-latency and secure performance demands of its enterprise and service provider customers.

Cyxtera Technologies operates over 50 data centres in major cities around the world, providing more than 3,500 customers with a secure global platform for mission-critical applications and systems.

“We continue to invest in best-in-class technology that supports the performance and security requirements of enterprise-grade connectivity,” said Damion Lackamp, senior director, Interconnection Products at Cyxtera Technologies. “As we expand our data centre facilities, the Infinera Groove solution provides the capacity, efficiency and security to boost the performance of our network infrastructure in a highly compact form factor.”

“With a highly compact and plug-and-play architecture, the Infinera Groove provides Cyxtera a proven foundation for programmable high-speed transmission, including a path to 600G,” said Pete Dale, VP, Cloud and Content Sales, Infinera.

Ayar Labs has announced that it has secured additional funding to fuel its growth as it drives to productize its TeraPHY optical I/O chiplets and SuperNova multi-wavelength lasers in 2019. The funding comes on the heels of the Optical Fiber Conference (OFC), where there was significant industry focus on the need for integrating silicon photonics based optical interconnect into semiconductor packages – a technique that promises to dramatically improve application performance, significantly reduce power consumption, and reduce overall datacenter platform costs for the Artificial Intelligence, High Performance Computing, Cloud, and Telecom markets.

“Silicon Valley Bank (SVB) has a long history of supporting promising technology companies,” said Lafe Vittitoe, Managing Director at Silicon Valley Bank. “Ayar Labs has everything we look for in an investment -- differentiated technology that addresses a large market opportunity, strong management and technology teams, and committed investors. We look forward to a long and fruitful relationship with Ayar Labs.”

The funding, which totals $3 million, comes in the form of a flexible draw down term loan and will be used on specific capital and manufacturing related expenditures as Ayar Labs ramps sampling and production. “SVB is a strategic long-term partner on our journey to bring our revolutionary technology to market,” said Charles Wuischpard, CEO of Ayar Labs. “Our customers and partners are excited at the progress we’re making; SVB’s investment will fuel our growth and accelerate our volume product introduction.”

Ayar Labs is also pleased to announce that it has been awarded a DARPA grant as part of the “Photonics in the Package for Extreme Scalability” (PIPES) program, a research initiative that seeks to develop high-bandwidth optical signaling technologies for digital microelectronics. Through the grant, Ayar Labs will work to accelerate the adoption and integration of the Advanced Interface Bus (AIB), a royalty-free high-bandwidth electrical interconnect standard, which will be used to link third-party chips to TeraPHY.

Additionally, to support its growing design win activities, Vladimir Stojanovic, a co-founder of Ayar Labs and Associate Professor of Electrical Engineering and Computer Science at the University of California at Berkeley, will be joining Ayar Labs in a full-time capacity to lead system architecture.

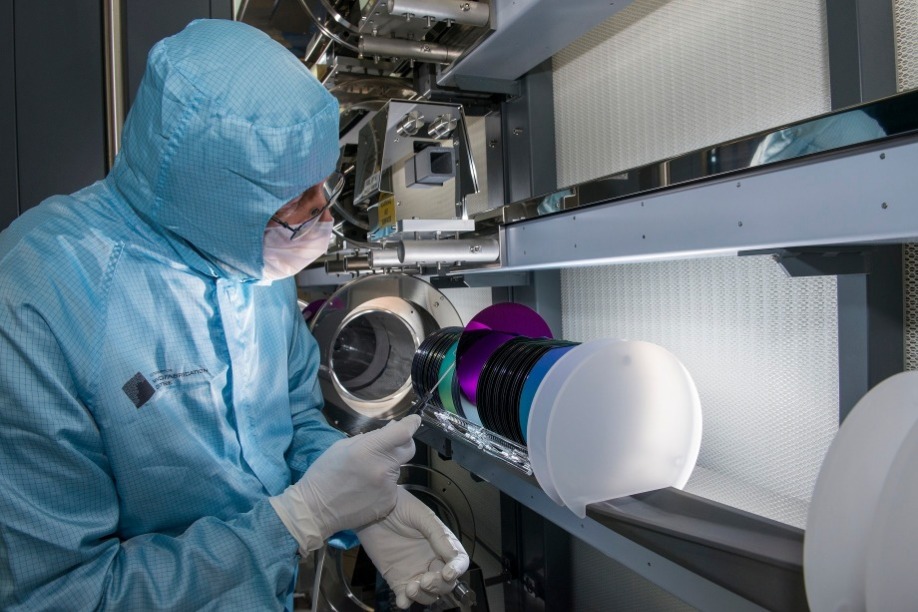

IQE has announced that its recently constructed Newport Mega Foundry has received its first mass production order from its leading existing VCSEL customer.

The achievement of full product qualification status is the result of extensive quality and process audits by the customer and their end OEM, as well as exhaustive product qualification trials including full reliability testing. Qualification of further tools is in progress and is expected to complete over the coming months.

In addition to the qualification with this customer, further VCSEL product qualifications are at advanced stages with more than ten other customers, two of which are expected to reach a successful conclusion over the next few weeks.

Customer feedback from the additional qualifications confirms the superior quality and performance from the new facility.

The Newport Mega Foundry is the largest outsource epi facility for advanced compound semiconductors globally and has been under construction for the last 18 months. It currently has ten large-scale production MOCVD tools installed, with space for up to an additional 90 tools. The manufacturing facility also houses an extensive suite of highly advanced wafer characterisation tools to ensure outstanding, world-class wafer quality.

The first ten tools are dedicated to 6 inch VCSEL production for end applications that include 3D sensing, high-speed datacoms, Advanced Driver Assistance Systems (ADAS), LiDAR, proximity sensing and Time of Flight (ToF) systems.

The market for VCSELs is expected to grow rapidly over the coming years as 3D sensing is installed across multiple user platforms, including facial recognition, world facing cameras for Augmented Reality (AR) and 3D photography, security cameras, industrial sensing and heating, ADAS, LiDAR, high speed datacomms and proximity sensing.

Drew Nelson, CEO and president of IQE commented: "I am very pleased to announce IQE receipt of full product qualification status from our leading VCSEL customer, and the first order for mass production from our new Mega Epi foundry in Newport.

"IQE has invested heavily, along with help from the Cardiff City Region Deal (CCR), to build the worlds largest outsource epi facility, demonstrating our commitment to providing the capacity required for large scale deployment of VCSELs and other Compound Semiconductor (CS) products, as the CS industry moves through a real inflection point in volume manufacture.

"IQE is committed to leadership of this mass CS scaling, offering a unique range of wafer products and complementary technologies, enabling our customers to introduce disruptive products to the end marketplace. We have a powerful and extensive roadmap for VCSEL technology, which we believe will help the acceleration of the deployment of VCSELs across many end applications".

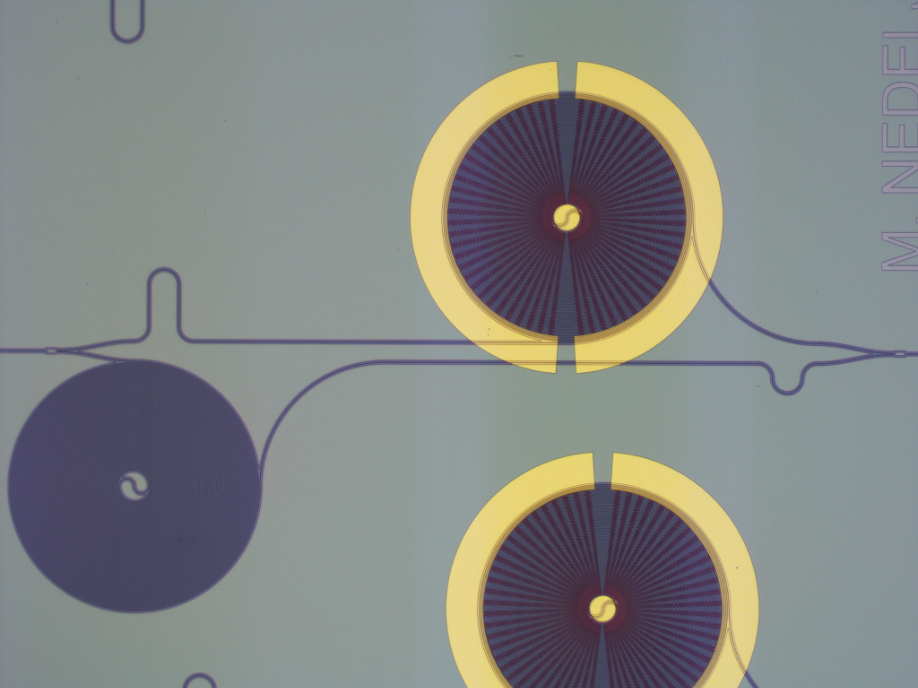

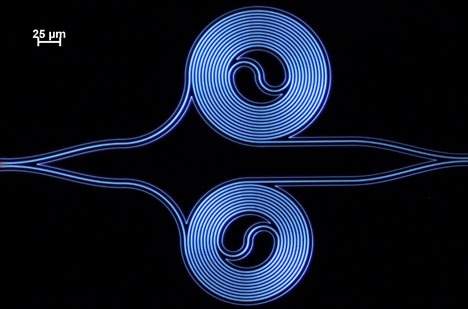

The Laboratory for Nanoscale Optics at the Harvard John A. Paulson School of Engineering and Applied Sciences is rapidly running down the checklist to develop ultra-efficient integrated photonic circuits. First, they developed a technique to fabricate high-performance optical microstructures using lithium niobate. Then, they designed an integrated frequency converter, an integrated modulator and a platform to store light and electrically control its frequency in an integrated circuit. Most recently, they designed on-chip, electronically driven frequency comb.

Now, the team of researchers — led by Marko Loncar, the Tiantsai Lin Professor of Electrical Engineering and Applied Physics at SEAS — has developed a chip-scale frequency comb system that can not only generate a comb, but also manipulate it on the same chip.

“Before this research, once we generated a frequency comb on a chip, we had to transfer the signals out of the chip and use off-chip components for further manipulation of the signals, which are usually bulky and expensive,” said Cheng Wang, co-first author of the paper, former postdoctoral fellow at SEAS, and now Assistant Professor at City University of Hong Kong. “Now, we can integrate all these additional functionalities onto the same chip as the comb generator, potentially realizing many different comb applications all in one chip.”

Optical frequency combs are lasers that emit multiple frequencies (colors) of light simultaneously, each precisely separated like the tooth on a comb. The researchers were focused on generating a specific type, known as a Kerr frequency comb, which has a range of applications in everything from optical clocks and spectroscopy to telecommunications and quantum information processing. While these frequency combs have been generated on-chip before, researchers have struggled to also integrate the components needed to manipulate the comb.

That’s where lithium niobate come in.

Loncar’s lab is pioneering the use of thin-film lithium niobate as a platform for integrated photonics. Its unique electro-optical properties make it possible to both generate the frequency comb on chip and manipulate it.

“This is the first time a Kerr frequency comb has been generated on a lithium niobate platform, and the first time that Kerr comb generation, filtering and modulation were all realized on the same chip,” said Cheng.

“We’ve shown that it is possible to integrate distinct photonic functionalities on a monolithic integrated lithium niobite chip, which could lead to a new generation of microcomb applications in spectroscopy, data communication, ranging and quantum photonics,” said Loncar, senior author of the study.

The Harvard Office of Technology Development has protected the intellectual property relating to this project. The research was also supported by OTD’s Physical Sciences & Engineering Accelerator, which provides translational funding for research projects that show potential for significant commercial impact.

This research was co-authored by Mian Zhang, Mengjie Yu, Rongrong Zhu and Han Hu.It was supported in part by the National Science Foundation, the DARPA SCOUT program, and the Harvard University Office of Technology Development Physical Sciences and Engineering Accelerator. The research was published in Nature Communications.

Synopsys has announced that PLASMOfab, a research project funded by the EU innovation program Horizon 2020, has been successfully completed to enable mass manufacturing of high-performance plasmo-photonic components. Launched in 2016, the project has brought together leading industrial partners and top-ranked academic and research institutes in the photonic integrated circuit (PIC) and opto-electronics value chain, including PhoeniX Software, now part of Synopsys' Photonic Solutions.

The three-year research project has significantly advanced the state of the art in PICs and CMOS-compatible plasmonics for optical data communications and biosensing for point-of-care applications. PLASMOfab has developed CMOS-compatible plasmonics to consolidate advanced PICs with electronic ICs in volume manufacturing. The project focused on CMOS-compatible metals and photonic structures that are harmonically co-integrated with electronics using standardized CMOS processes. As part of project validation, the PIC platform was used along with advanced peripherals to develop predominant functional modules with unprecedented performance.

A key project achievement was the development of a groundbreaking ultra-compact plasmonic transmitter, which has a footprint of 90 x 5.5 µm² to transmit 0.8 TBit/s (800Gbit/s) through 4 individual 0.2 TBit/s transmitters. The project also demonstrated CMOS-compatible plasmonic waveguides with the lowest possible losses, as described in Nature's Scientific Reports in September 2018.

"PLASMOfab's main goal has been to address the ever increasing needs for low energy, small size, high complexity and high performance mass manufactured PICs," said Nikos Pleros, assistant professor at the Aristotle University of Thessaloniki, Greece. "We have achieved this by developing a revolutionary yet CMOS-compatible fabrication platform for seamless co-integration of active plasmonics with photonic and electronic components."

As a result of the PLASMOfab research, two new companies have been launched to commercialize the new technologies:

bialoom Ltd will further explore plasmo-photonic biosensors in multichannel and high-sensitivity point-of-care diagnostics by combining plasmonic sensors with integrated Si3N4 photonic functionalities, electrical controls, biofunctionalization techniques, and microfluidics.

Polariton Technologies Ltd. specializes in new photonic and electronic technologies for the testing, sensing, and telecommunications market. Their energy efficient and low-footprint plasmonic modulator will convert microwave signals to optical signals.

"We expect that further development of CMOS-compatible plasmonic components with CMOS fabrication processes and photonics technologies will demonstrate plasmonics' clear advantages in PICs," said Dr. Dimitris Tsiokos, principal researcher at the Aristotle University of Thessaloniki. "When the best of all three worlds of plasmonics, photonics, and electronics converge in a single integration platform, PICs with unprecedented performance and functionality will be realized, targeting a diverse set of applications and industrial needs while meeting mass production requirements."

"We are pleased to have been working closely with the partners in this project and especially with AMO and ams to develop R&D PDKs for the new PLASMOfab integration technology," said Twan Korthorst, director of Synopsys' Photonic Solutions. "The PDKs are supported by our PIC design platform, which provides the industry's only full design flow from photonic device level to PIC to system levels."

The 2019 PIC International Conference honored outstanding innovators and excellence across the photonic integrated circuits ecosystem with its third annual PIC Awards presented recently in Brussels, Belgium. Honorees received awards based upon thousands of votes cast by persons working at institutes, universities and the global photonics industry to honor the best in PIC research, product and manufacturing equipment development, materials science and leadership.

Accepting the award on behalf of Prof. Reed was Dr. Callum Littlejohns from the University of Southampton’s silicon photonics programmes.

Professor Graham Reed, University of Southampton, was recognized for his foundational contributions to silicon photonics (SiP) and continuing leadership across the industry. He is presently the Deputy Director of the Optoelectronics Research Centre (ORC) and Director of CORNERSTONE—a rapid prototyping, multi-project wafer (MPW) programme also housed at the university that benefits companies and researchers developing new photonic integrated circuits (PICs). The group’s fabrication capability is funded by the Engineering and Physical Sciences Research Council (EPSRC), and collaboratively supports photonics research and manufacturing development programmes in the UK.

Upon winning the award Reed said, “I’m delighted and honoured to receive this award, especially because it was voted for by the silicon photonics industry. Given the buoyant field in which we all work, with so much talent around, it’s a testament to the great job the CORNERSTONE team have done at Southampton.” He added that while the PIC Award is tied to his pioneering SiP work, and in particular the CORNERSTONE project, the field itself and core photonic integration technologies grew as collaborative efforts utilizing II-VI / III-V materials and fabrication technologies.

Reed has dedicated much of his professional career to developing devices that today play a pivotal role in the growing photonics integration industry. He established the first Silicon Photonics Research Group in 1989 at Surrey, later moving programme components to Southampton. A noteworthy outgrowth of his early work was the establishment of the first silicon photonics company, Bookham Technology, which was led by former student, Dr. Andrew Rickman, now CEO of Rockley Photonics. Bookham is now part of Lumentum Holdings, a leading supplier of integrated photonics products to telecom and datacom networks. Amongst many accomplishments in silicon photonics, Reed’s team pioneered the pre-emphasis technique; the first 1 GHz modulator design and the first depletion modulator design that evolved into an industry standard. The team also pioneered industry-leading efforts that include creating the first 40GB/s modulator with high extinction ratio; the first 40Gb/s polarisation independent modulator; the first slow wave modulator, and the first 50Gb/s modulator.

CORNERSTONE has scheduled MPW runs throughout the year, with the next being on their SOI 500 nm platform with a June announcement of the design rules. This MPW run will be followed by a 220 nm SOI platform opportunity that has an August announcement. Check the organization’s website for further details at www.cornerstone.sotonfab.co.uk, or send an email to this address: cornerstone@soton.ac.uk.

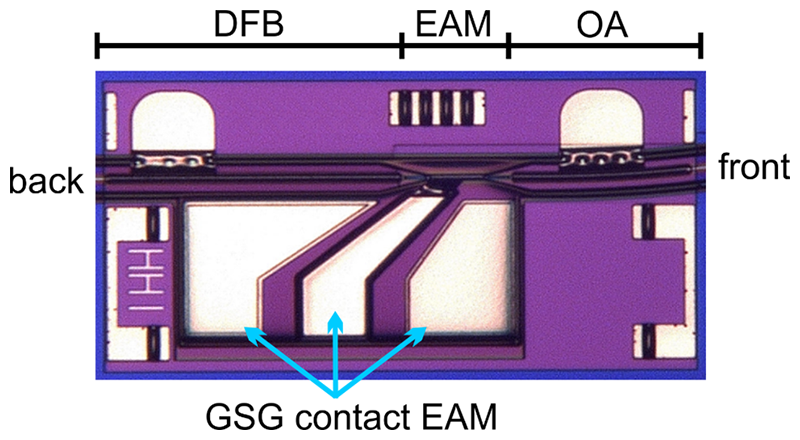

Martin Schell was recognized for a professional career dedicated to the advancement of optical science, photonic integrated circuits (PICs), and related technologies essential to present and future high speed data, telecom and video applications. He is chairperson for Optic and Optoelectronic Integration at the Technical University of Berlin and Executive Director of the Fraunhofer Heinrich Hertz Institute, also in Berlin. He is a board member of the European Photonics Industry Consortium (EPIC), as well as OptecBB (Competence Network for Optical Technologies in Berlin/Brandenburg, Germany), and a member of the Photonics21 Board of Stakeholders. Under his direction, the Photonic Component Department (PC) researches optical chip designs and photonic integrated circuits (PICs) for 100Gbps (and beyond) data transmission, detection and sensor applications.

Schell has successfully lead several photonic integrated circuit programs from idea to installation in the field. According to colleagues, he always attempts to be a voice of reason when it comes to evaluating various photonic integration approaches and their economic potential.

Together with international partners from research and industry, Fraunhofer HHI works across the whole spectrum of digital infrastructure – from fundamental research to the development of prototypes and solutions. The institute participates in the standardization of information and communication technologies and creates new applications together with industrial partners.

The Fraunhofer HHI focuses on 10 to 100Gbps transmission in the field of high-performance telecom components. In the area of mobile broadband systems, the organization concentrates its development activities in the areas of signal processing, wireless links and system optimization. Fraunhofer HHI also focuses on optical wireless communications to enable high-speed, short-range links within network systems, especially in environments where electromagnetic compatibility and security are of special concern.

Other primary Fraunhofer HHI research topics are in the area of video- and audio-coding and transmission. The Fraunhofer HHI makes a significant contribution in the fields of greater efficiency in compression methods, autostereoscopic 3D displays and in the integration of real and virtual worlds for immersive multimedia applications.

Best New PIC-Enabled Product or Achievement in Non-Optical-Fibered Modules

CARDIS, a €3.6 million EU-funded project that is part of the Horizon 2020 program, was recognized for its use of silicon photonics (SiP) as a means to support the early detection of cardiovascular disease (CVD). Partners within the consortium developed a new photonics-based, non-invasive test to screen for CVD that is showing promise in early clinical trials. The CARDIS effort was coordinated by SiP specialists at imec in Belgium. The team has developed a handheld laser Doppler vibrometry (LDV) prototype that has been used successfully in initial clinical trials. Other key partners include the medical device developer and manufacturer Medtronic; researchers at Ghent University in Belgium; the Tyndall National Institute in Ireland; Queen Mary University of London, and the University of Maastricht in the Netherlands.

Identification of individuals at risk of CVD at its earliest stages allows for intervention to halt or reverse the pathological process, according to researchers. Assessment of arterial stiffness by measurement of aortic pulse wave velocity (aPWV) is included in the latest guidelines for CVD risk prediction. Prior to the development of the CARDIS prototype, no medical instrument has been available to screen large populations based on the measurement of aPWV due to the high cost and difficult operational procedures needed with legacy instruments. The goal of CARDIS is to change this situation by providing a cheaper, PIC-based device to measure patients’ aPWV by operators needing only modest levels of training; this is expected to help reduce overall medical costs and risks to patients’ long-term health.

The prototype device has proven to be easy to use in a clinical feasibility study involving 100 patients. The quality of the device readings was found to be very good. In carotid-femoral PWV measurements (the so-called ‘gold standard’ to estimate arterial stiffness,) the performance of the PIC-based device was found to be as good as that of commercial PWV-measurement devices, according to initial tests. The CARDIS device is now undergoing further evaluations to help simplify testing and operational procedures; another clinical study is planned at the Academic Hospital of Maastricht.

To make a PWV measurements, a very low-power laser is directed towards the skin above an artery. A patient’s heartbeat pattern is then determined based upon the Doppler shift of the beam reflected by the skin. At the heart of the multi-beam LDV system is a silicon photonics chip designed by the Photonics Research Group team at Ghent University that was prototyped using imec’s in-house silicon photonics pilot facility.

Best New PIC-Enabled Product or Achievement in Optical-Fibered Modules

PHIX Photonics Assembly was honored for its continuing efforts to automate and simplify test, assembly and packaging (TAP) systems for photonic chip manufacturing. PHIX was founded in 2017 by LioniX International. PHIX offers a cost-effective manufacturing service for photonic integrated circuit (PIC)-based modules in large volumes. PHIX is located at the High Tech Factory in Enschede, the Netherlands. PHIX offers assembly services for all three major PIC technology platforms (InP, Si and TriPleX) and is specialized in hybrid integration of multiple PICs in one module, both with optical fiber interfaces as well as free space optical interfaces through micro optical components.

At the time of its founding, PHIX said it would work in close cooperation with the Fraunhofer Project Center on packaging standards for high-volume manufacturing of integrated photonics modules, and with PhoeniX Software (now a division of Synopsys) in developing the appropriate photonic design kits dedicated to assembly and packaging.

Hans van den Vlekkert, the CEO of LioniX International who helped to established PHIX, emphasised the need for a strong regional ecosystem for integrated photonics, where education, development, production and volume production go hand in hand.

“We have seen accelerated growth of integrated photonics market over the past year, especially for the demand of devices that are based on our low-loss TriPleX platform. We have delivered many prototypes to international customers and anticipate volume demand for the PIC modules … which requires an efficient organisation, such as PHIX B.V., where the infrastructure and production flow are tailored to achieve cost-effective assembly and packaging of PIC modules.”

Best Achievement in PIC Platform

Lightwave Logic was honored at the third PIC Awards for development of its 100GHz photonic integrated circuits (PICs) platform based on the company’s high-performance Perkinamine™ polymer materials which target the insatiable demand for fast data communications in the multi-billion-dollar telecom and data markets supporting media streaming, AI (artificial intelligence) and IoT (Internet of Things).

With photonics continuing to penetrate deeper into networking applications, polymers are seeing increased applications due to their unique material properties, compatibility with existing fabrication methods, equipment and devices. Polymers also have the potential to impact non-communication markets such as sensing, LIDAR/automotive, and medical/healthcare.

Unlike most polymers used in passive photonics today, Lightwave Logic’s Faster by Design™ technology is a very high-speed active integrated optics technology that has similar capabilities to semiconductor platforms but is capable of extension to higher speeds and lower electrical power consumption.

The PIC International Conference created its PIC Awards to put the spotlight on innovation and key industry advances in photonic integration through platform development, manufacturing, design, packaging and device characterization. Lightwave Logic participates on all these fronts including engineering and synthesis of its polymer materials. The company recently announced a new material with double the electro-optic activity as its prior material. Increased electro-optic activity is important as it directly affects modulator drive voltages and consequently enables lower power consumption. Results achieved to date point to the great remaining untapped potential of engineered polymer materials.

Dr. Michael Lebby, CEO of Lightwave Logic, accepted the award at the ceremony in Brussels. He noted, “I am truly proud and privileged to be able to accept an internationally recognized award for our polymer technology platform on behalf of all of Lightwave Logic. The team has worked very hard in developing innovative, high performance, power-efficient materials and devices for the internet, and this award is a testament to the quality of their work.”

Lightwave Logic, Inc. is a development stage company moving toward commercialization of next generation photonic devices using its high-activity and high-stability organic polymers for applications in data communications and telecommunications markets. Photonic electro-optical devices convert data from electric signals into optical signals. For more information about Lightwave Logic, please visit the corporate website at lightwavelogic.com.

Best Achievement in PIC Development

VLC Photonics was honored for its outstanding contribution to the creation and support of the ecosystem for fabless PIC development. The company has been serving the industry for the last eight years by providing photonic integration services to many customers in different markets. In this period, VLC Photonics has pioneered the design house business model for photonics, building a brand that is well recognized as a symbol of expertise, professionalism and independence. Its technical works (when publication is possible while adhering to confidentiality agreements with its customers,) have been published in more than 50 scientific conferences, industrial magazines and peer-reviewed journals, including the prestigious Nature and Optica.

The company has designed and taped-out photonic integrated circuits at 20 different foundries on all the main material platforms, including silicon photonics, silicon nitride, indium phosphide and PLC. Many photonic building blocks have been developed and validated into proprietary libraries and Process Design Kits (PDKs), including arrayed waveguide gratings, multi-mode interference couplers, Echelle gratings, ring filters, tunable lasers, etc. Its designs are now enabling commercial optical transceivers and interconnects, fiber sensor interrogators, quantum cryptography devices and many more.

Recently, VLC Photonics trained a team and invested more than 600,000 euros in equipment to better serve its customers at the chip characterization and testing stages. Such tests are still one of the main bottlenecks when moving from prototyping to production, and VLC Photonics has successfully achieved becoming a photonic test house that supports the full design-to-test cycle in a flexible and semi-automated way. Moreover, VLC Photonics’ characterization capabilities span from the infrared range, typical of telecom and datacom applications, down to the near infrared and visible wavelengths, which are more frequently used in biophotonic, LiDAR or quantum applications.

VLC Photonics has also been reported upon in more than eight market reports from different sources as one of the key players of the ecosystem. The company and its founders have received many awards and recognitions in the last years. It has partnered with the main photonic EDA companies, the largest foundries and pioneering photonic packaging houses as well. These partnerships enable offering turn-key solutions to customers in a seamless and efficient way. Its customer base ranges from small technology start-ups to large Fortune 500 corporations, and has been steadily growing and consolidating along the years.

Building on the success of its predecessors, the fourth Photonic Integrated Circuits (PIC) International Conference pinpointed the most promising opportunities for this industry. More than 700 attended the co-located conferences that focused on advances in PICs, compound semiconductors and the future of advanced sensor solutions.

Conference Co-Chairs, Dr. Michael Lebby and Dr. Bill Ring, praised the leadership and organization of the fourth photonic integrated circuits (PIC) International Conference that took place 26-27 March in Brussels. 2019 marked the fourth consecutive year of growth, with more than 700 attendees and 70 sponsors joining to hear from industry leaders focused on advanced technologies driving the future of global business.

"We have just finished the fourth annual PIC International Conference, and again like in 2018, it surpassed everybody's expectations. But what's more, folks are now recognizing throughout the value chain, from wafers to epitaxial growth, devices, packaging, modules and systems, to social media that PIC International is the conference to attend if your interest is photonic integrated circuits (PICs). We again filled all of our seats, and like last year folks from CS International and SSI attended the PIC sessions. Our annual PIC awards generated nearly 10,000 online votes and the winners in six categories were announced at the end of Day One by the European trade association, EPIC. In (our) humble opinion, this was the best PIC International event to date, and achieved not only world class speakers, world class presentations, but also world class networking during the exhibit hours, breaks, and meal events,” remarked co-chairmen, Dr. Michael Lebby and Dr. Bill Ring following the event.

The prestigious PIC industry awards entered their third year. Winners were voted for by the PIC industry and include the following honorees:

Individual Awards:

1) PIC Lifetime Achievement award - Professor Martin Schell

2) PIC Individual Contributor award - Professor Graham Reed

Company Awards:

1) Best Achievement in PIC development - VLC Photonics

2) Best Achievement in PIC platform - Lightwave Logic

3) Best new PIC-enabled product or achievement in optical-fibered modules - PHIX

4) Best new PIC-enabled product or achievement in non-optical-fibered modules: H2020-Project CARDIS http://www.cardis-h2020.eu/

In 2019 more than 700 delegates attended two days of jam-packed (and at times, standing room only) sessions on photonic integrated circuits (PICs) that focused not only on innovative technology, but how PICs could alleviate major headaches that optical networks, datacenters, telecommunications systems and related applications see today. Many talks focused on how PICs could be implemented into novel and innovative applications to move the industry forward while at the same time providing the long-term scalability needed to grow an industry for decades to come. As in 2018, one of the biggest drivers for PICs are fiber optic communications for datacentre interconnects. Facebook spoke about the huge opportunities for innovative solutions within their datacentres that addressed high speed, low power consumption, innovative packaging (via co-packaged solutions), reliability, and cost effectiveness. Companies like Facebook are looking for PIC leadership, quality and reliability in their bid to replace slower, lower bandwidth legacy systems that are already creating data bottlenecks.

There were also talks that explored PIC based technologies outside of fiber optics including biologic and health monitoring/diagnoses, medical, sensing, and LiDAR for automotive applications. One of the most promising segments for PICs is 3D sensing, especially face recognition for mobile phones.

This year's conference brought together luminaries of the PIC industry who participated in two panel sessions: the first on Day One addressed high volume, high performance PICs for fiber communications; the second on Day Two explored the merits of manufacturing PICs using shared foundries and pilot lines from all over the world. Panel members represented PIC design and manufacturers from Japan, the USA and Europe. The panel sessions generated interesting themes such as: PICs for datacentres are already entering service; PICs for telecom are a quickly growing opportunity; PICs for non-communications markets also rapidly expanding.

In a sense, the Day One panel emulated what was being said in the PIC talks: New and innovative solutions to PIC packaging are urgently needed. One solution advocated by panelists is generally referred to as co-packaging - a way to package PICs along with electronics as a means to bring the photonics closer to the electronics and thereby achieve higher switch capacities on a line card in a datacentre. Today, the popular solution is to use pluggable transceivers mounted into a faceplate. Speakers said that for tomorrow, they supported solutions to use not only on-board optics, but co-packaged optics driven by PIC technological platforms.

The Day Two panel session focused on PIC foundries and their eco-system. Panelists were questioned on the business aspects of running a PIC foundry, the volume needed for sustainability, and the impact on MPW (multi-project wafers) or sharing costs so that SMEs (Small and Medium-sized Enterprises) can participate. Comparisons were made with the silicon industry that has developed a strong foundry model over the past 30 years. In photonics, and in particular PICs, the photonics foundry model is just developing and still in its infancy. Panelists discussed the merits of what photonic PIC foundries need to assist in success. One area that was frequently raised during both panel session discussions and in foundry-based presentations was volume. While GaAs VCSEL-based PICs are experiencing consumer success and volume activity with the application of structured light for optical sensing, other PIC-based applications are not consumer based and as such similar high volumes have yet not materialized. Silicon photonics has the potential to drive costs very low with 200mm and 300mm wafers and is still looking for a high-volume vehicle. Indium phosphide PICs are on smaller wafers (75mm and 100mm) and also would like to see high volumes and even larger format wafers at 150mm.

The conference discussed in detail incumbent PIC technologies such as InP and GaAs, as well as Silicon Photonics (SiP), Polymer Photonics (PP), and Dielectric Photonics (DP). Silicon photonics continues to grow in use and popularity with companies such as Intel, Hewlett Packard Enterprise, AIM Photonics, and Rockley Photonics showing the impact of silicon economics. Infinera and Ciena showed very high-performance PIC results on indium phosphide, while companies such as Broadex and LioniX showed significant progress with dielectric photonics. Lightwave Logic also reported their results with very low voltage, very high bandwidth polymer device designs.

The conference also discussed both datacentre and telecommunications opportunities for PICs with forecasts for new architectures, standards, technologies and cost expectations. The latest results in the PIC field were also presented and showed a significant performance upgrade towards transceivers at 400Gbps while some speakers spoke about a future aiming towards 800Gbps, 1600Gbps and beyond.

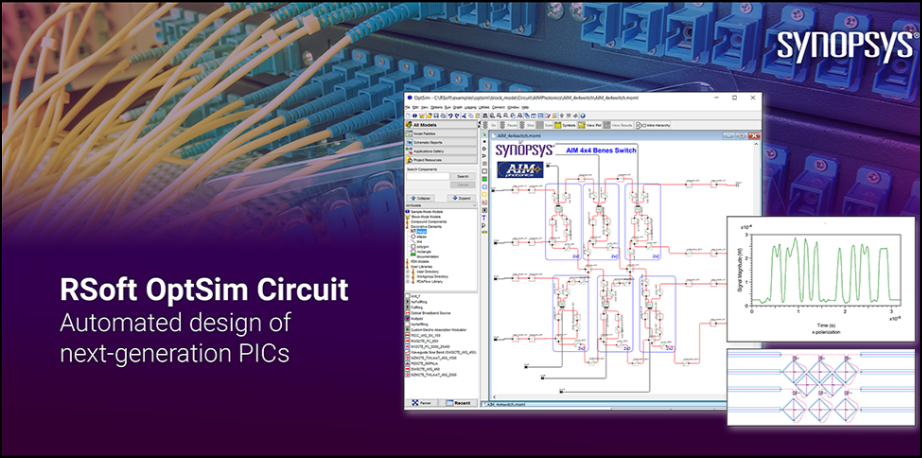

There were a number of exciting sessions, including those that emphasized the role of software tools for modelling, simulation, and production. One session discussed improvements in PIC infrastructure for designing and manufacturing robust and reliable PICs using the latest in advanced software design tools. This was supported by many PIC talks that addressed PDKs and other metrics needed to quickly grow PIC markets.

This year, new and innovative talks discussed how PIC-based technologies can enable new products that have smaller form factors, low power, and high performance, which is becoming especially important for hand-held battery powered diagnosis and health monitoring products. CARDIS, an EU-funded program and 2019 PIC Award winner, is one example of using SiP PICs for medical diagnosis.

Conference speakers also addressed new opportunities that can arise as the result of designing PICs for telecommunications and datacom applications and the ways in which these telecom/datacom PIC designs could easily be applied to medical, measurement, automotive, and other industrial applications. Perhaps by next year's PIC International Conference we will see the first products emerge in these new market segments.

Conference speakers also shared the good news that a number of emerging opportunities for PICs will be high volume, such as GaAs VCSEL arrays for sensing (as used by mobile phones). They emphasized that opportunities in consumer markets for PIC-based technologies are only just beginning to be realized, and we will have to wait to see how the extreme high-volume ramps will play out over the next year and beyond.

All presentations showed a number of improvements in the technology over the past 12 months. PIC markets are growing strongly to tens of billions of euros over the next decade, while the scalability of PIC technological platforms is also expected to significantly increase. The rise of the hybrid PIC, the co-packaged platform, and shared foundries as noted by conference panelists showed that customers are now more open than ever to find the right PIC solution for their particular portfolio and market requirement.

“A focused and well attended conference, with a high level of technical content, PIC International surpassed itself again in 2019. PIC International is the conference to attend for the latest and greatest in photonic integrated circuits; it has become a truly global event. 2020 in Brussels, Belgium should be even better than 2019 and truly world-class – We look forward to next year with anticipation."

Michael Lebby and Bill Ring

Co-Conference Chairs

We are delighted to announce that the dates for PIC International 2020 are confirmed for Tuesday 31st March and Wednesday 1st April.

With many sponsorship and exhibition opportunities already secured for next year's show, make sure you don't miss out! Email: info@picinternational.net or call +44 (0)24 7671 8970.

Silicon photonics pioneer Graham Reed was honored with a 2019 PIC Award for individual contributions to the industry he helped create. While Reed accepts the accolades, he is quick to point out that his accomplishments, and the CORNERSTONE programme at the University of Southampton, have been and always will be a team effort.

New applications and markets regularly emerge for silicon photonics (SiP) and related technologies that have been foundational to the development and evolution of photonic integrated circuits (PICs). Pioneering individuals and companies they founded recognized the potential of utilizing low-cost silicon fabrication techniques and processes for optical and digital data applications. Their work revolutionized ‘business as usual’ and along the way they created an industry.

What was not too long ago seen as an emerging technology is now at work in datacenters and telecom networks as part of transceiver modules and switches or playing key roles in other digital data components. The performance gains, size reductions and power savings of using photons in place of electrons to transmit and receive data continues to grow.

Professor Graham Reed, University of Southampton, was honoured with a 2019 PIC Award for individual contributor accomplishments. Speaking with Reed after the awards were presented at the PIC International Conference in Brussels, he noted that although the PIC Award is tied to his pioneering silicon photonics (SiP) work, and in particular the CORNERSTONE project, the field itself and core photonic integration technologies grew as collaborative efforts utilizing II-VI / III-V materials and fabrication technologies.

“When I started in this area, it wasn’t even called silicon photonics…we called it integrated optics in silicon, but what the name meant was actually that silicon was primary, and not much else was present besides some germanium used in the detector. We were thinking of sensor networks for the first application, and those are now coming about. But almost from the start the field involved integration, like the light source, which brought in III-V materials. And today we are looking at all sorts of materials, modulation schemes and ways you can combine polymers into different sorts of waveguides. So when you consider how the field has grown and changed today, a better name might be silicon compatible photonics,” he said.

Reed has dedicated much of his professional career to developing devices that today play a pivotal role in the growing photonics integration industry. He established the first Silicon Photonics Research Group in 1989 at Surrey, later moving programme components to Southampton. A noteworthy outgrowth of his early work was the establishment of the first silicon photonics company, Bookham Technology, which was led by former student, Dr. Andrew Rickman, now CEO of Rockley Photonics. Bookham is now part of Lumentum Holdings, a leading supplier of integrated photonics products to telecom and datacom networks. Amongst many accomplishments in silicon photonics, Reed’s team pioneered the pre-emphasis technique; the first 1 GHz modulator design and the first depletion modulator design that evolved into an industry standard. The team also pioneered industry-leading efforts that include creating the first 40GB/s modulator with high extinction ratio; the first 40Gb/s polarisation independent modulator; the first slow wave modulator, and the first 50Gb/s modulator.

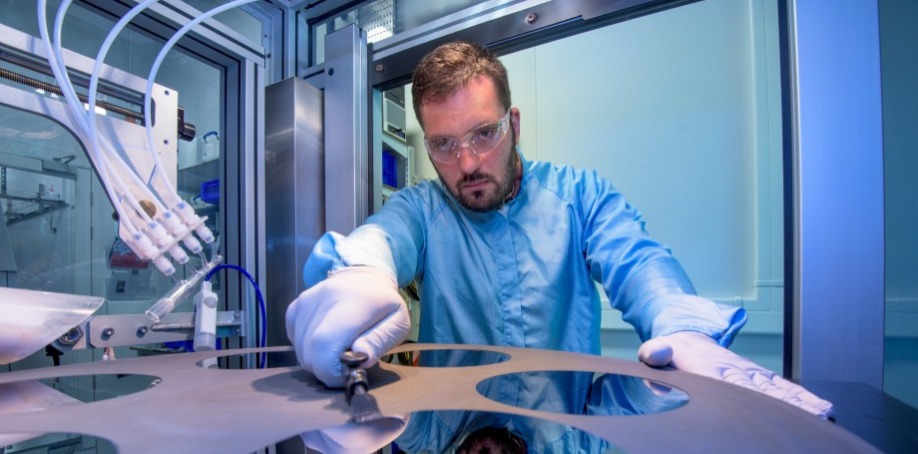

Reed is presently the Deputy Director of the Optoelectronics Research Centre (ORC) at Southampton and Director of CORNERSTONE—a rapid prototyping, multi-project wafer (MPW) programme also housed at Southampton that benefits companies and researchers developing new photonic integrated circuits (PICs). The CORNERSTONE project is funded by the Engineering and Physical Sciences Research Council (EPSRC) and is part of collaborative photonics research and manufacturing development programmes in the UK involving universities at Glasgow, Southampton and Surrey. Device fabrication at wafer scale is conducted primarily in Southampton’s ORC cleanrooms, and at chip scale in Glasgow.

Research into photonic integration, design and fabrication are central to the ORC’s on-going programmes, while device fabrication (for research and for prototyping devices destined for manufacturing,) is central to CORNERSTONE’s mission. A third area that is seeing rapid development is bespoke training courses offered primarily through facilities based in Southampton that focus on the needs of companies and their workforces for advanced photonic design and fabrication. The Higher Education Funding Council for England provided the economic resources to establish the training course development that Reed notes is growing rapidly.

Bespoke training can be tailored to support needs in any aspect of PIC design, and is offered in parallel with the CORNERSTONE MPW capabilities. Members of the training team work with companies to build a curriculum around precise requirements, offering the flexibility to specify which topics should be covered along with the training schedule, duration and related factors. Potential topics include:

Participants have the chance to visit Southampton’s cleanroom complex and experience live device fabrication using advanced, industry-compatible, deep-UV projection lithography and related tools.

Training can be integrated into any of the CORNERSTONE MPW fabrication batches on various silicon-on-insulator (SOI) platforms, including state-of-the-art modulator design, fabrication and characterisation, or offered as a stand-alone course.

“At a higher level we are looking at options to continue enhancing what we offer at CORNERSTONE. Part of this applies to devices we fabricate and how that can apply to the courses and training that we provide… For example, we design our own electronic modulator drivers, and then we flip chip them onto the SiP, and this would allow us to offer electronic / photonic integration through CORNERSTONE. We also want to offer pick and place, and then more platforms that could be incorporated into SiP…We are developing a silicon nitride platform, an undercut silicon platform for mid infrared (MIR) applications, and a germanium on silicon platform that supports longer MIR wavelengths up to 14 µm. We would like users at CORNERSTONE to access as much of this technology as possible, so flexibility is a key to offer more, but without undercutting our partners or customers,” Reed remarked.

As he explained, the CORNERSTONE programme has grown rapidly; it is now onto its thirteenth call. “It’s a user driven process,” noted Reed. “It has taken off quite quickly – we have only been offering CORNERSTONE fabricated devices just over two years, and one thing that the users have said is that it’s a great program, but can you offer more platforms and functionality? We are looking for ways to offer things through CORNERSTONE which have been developed as part of our other research projects, and ways that we can expand the programme…But as complexities increase we have to be sure everything fits together.”

One recent participant that plans a return engagement in Southampton and the CORNERSTONE programme is Dr. Iain Crowe, Associate Professor in Electrical and Electronic Engineering at the University of Manchester (UK). Crowe utilized CORNERSTONE’s MPW programme after previously working with SiP foundries elsewhere in Europe and Asia.

“The facilities in Southampton are world class and the personnel highly professional and expert in silicon photonics. The CORNERSTONE programme has helped establish this facility as the UK leader in silicon photonics MPW fabrication, contributing to the successful delivery of a number of other (UK and internationally) funded research programs,” Crowe said.

An important aspect of Crowe’s work that was facilitated through CORNERSTONE was the design verification process that aided the efforts of students and faculty by ‘de-risking’ a number of their designs.

“We have used the facility now more than once and although these are prototyping runs for research purposes, as our understanding of certain designs matures we certainly will be considering how these can be scaled up for future manufacturing and will seek the support at the ORC to help us streamline this,” Crowe explained. “In fact, we have just submitted another set of designs as part of MPW number 12, which will be a crucial step in helping us to deliver our own EPSRC-GCRF funded contract.”

Accessing world-class facilities for research, product development and making the move to volume manufacturing requires high-quality materials as well as skilled expertise and the latest process tools. Stuart Edwards, Business Development Director at IQE, said he continues to be impressed with the range of services and expertise offered through CORNERSTONE. IQE manufactures advanced epitaxial wafers for a wide range of applications for wireless, optoelectronic, electronic and solar devices; the company is headquartered in Cardiff, Wales. IQE, with fabrication locations in the UK, the United States and Asia, said it sees the combination of services and training offered through CORNERSTONE as a key resource for building a UK/European integrated photonics industry.

“IQE has been involved in the development and supply of advanced epitaxy material for many years for use in the fabrication of silicon photonic devices, both for low TRL activities with universities and product level processes for commercial customers. As the field develops and continues to grow we are committed to remain a key supplier in the market and as part of this we were keen to leverage the benefits of the knowledge of Graham and his team in Southampton. After becoming aware of the CORNERSTONE programme and the options available for bespoke training, we are exploiting this across our development, operations and commercial teams to improve our focus in this area and better serve our customers.”

Looking ahead to the future of both photonic integration research and device design, Reed said that one of the most rewarding aspects of working through CORNERSTONE, and their many partners and customers, is the way that one product or device idea leads to another. Constant feedback and new ideas generated by MPW runs, as well as interaction with training course participants, drives the potential to expand what CORNERSTONE offers.

“We always look for ways to incorporate what we are doing in our own research into what we can offer through CORNERSTONE and MPW runs, but you have to get down to a much deeper level of detail. There are many ideas about what we might be able to offer and integrate, yet we need to make certain that we can fully develop these offerings and truly make them available, and this takes time…In principle some new things we try will work for our own applications or in the lab, but we want to make certain the process works for the majority of what our customers’ purposes might be and that all we offer is compatible,” he explained.

After more than 30 years in a field he helped pioneer, Reed looks forward to the continuing challenges, even though he finds that with the growth and expansion of the organization’s programmes, he’s more of an administrator than he might like to be on a given day. “In some fields one does his part, but seldom gets to see it from the start. I am fortunate in that I could help start a field and then get to watch it evolve; it’s all interesting stuff. I like to see something that we develop and then see how others take it in different directions or see different possibilities, like going to a conference where you hear a presentation and you realize it was something that started with our research…It’s quite amazing.”

“As you know, one of my former students, Dr. Andrew Rickman, went on to found Bookham Technology that’s now part of Lumentum. We worked with Bookham for more than a decade, but eventually they got out of SiP and I was wondering if ‘that was it’ around 2000. About two weeks later, Intel rang and said that they had a programme for silicon photonics, and that was the beginning of my work in their programme as a consultant. I saw what they were putting into it back then. After a while you realize that this thing—SiP—has legs to it after all.”

Indeed it has. CORNERSTONE has scheduled MPW runs throughout the year, with the next being on their SOI 500 nm platform with a June announcement of the design rules. This MPW run will be followed by a 220 nm SOI platform opportunity that has an August announcement. Check the organization’s website for further details at www.cornerstone.sotonfab.co.uk, or send an email to this address: cornerstone@soton.ac.uk.

The silicon photonics revolution is gathering pace, thanks to the introduction of powerful lasers that don’t require an insulating intermediary layer

BY DONGJAE SHIN AND KYOUNGHO HA FROM SAMSUNG ADVANCED INSTITUTE OF TECHNOLOGY, SAMSUNG ELECTRONICS

Back in the middle of the twentieth century, a revolution took place in the electronics industry. Out went the vacuum tube and in its place came the integrated circuit.

Now this industry is starting to embark upon another major change. There is a shift to the optical domain, driven by scalability limitations associated with some electric ICs, along with the promise of newly emerging applications. To usher in this new era, money is pouring into silicon photonics technology, enabling the integration of photonic devices.

Part of the motivation behind this investment is that there are several applications where the addition of photonic ICs could aid ‘mother’ electric ICs. They include CPU-memory interconnects, an opportunity that has been discussed for several decades.

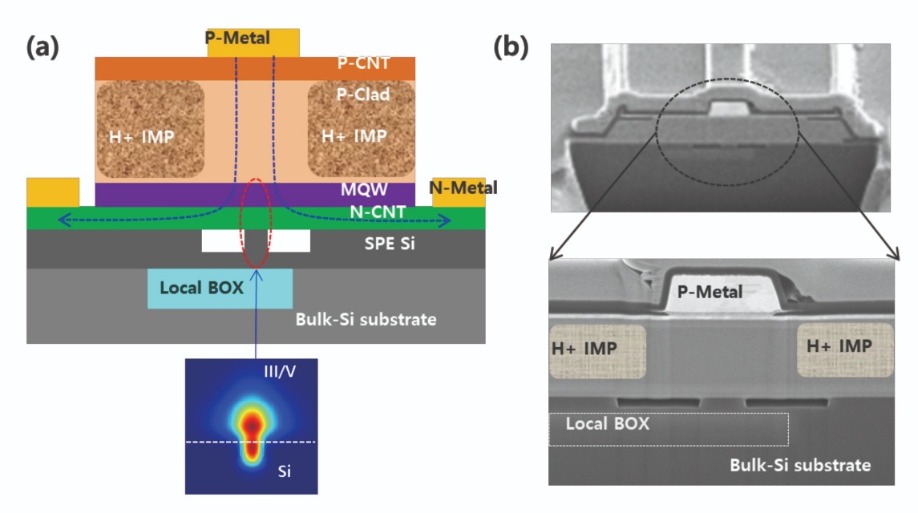

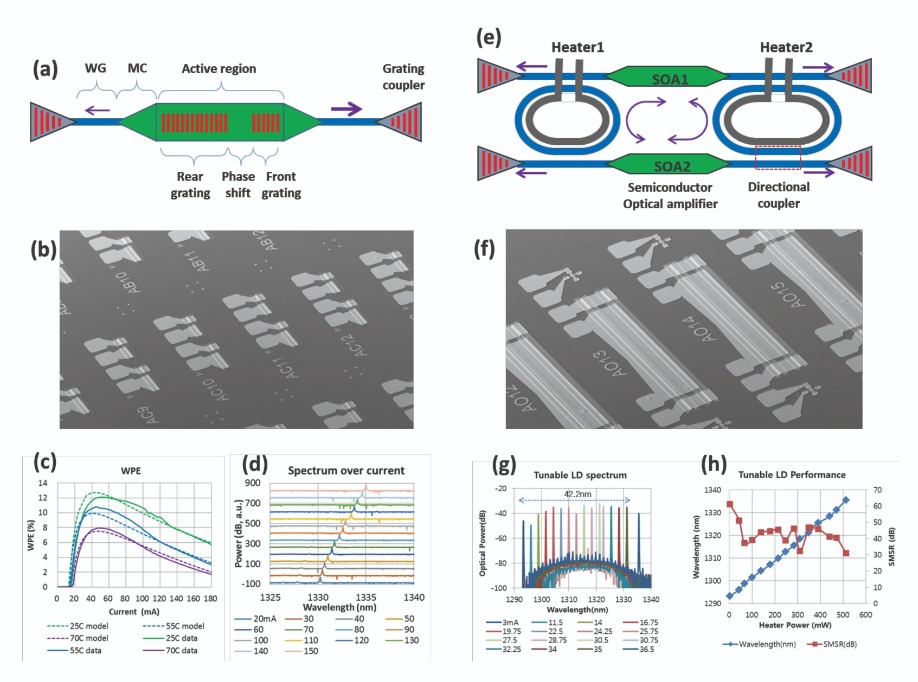

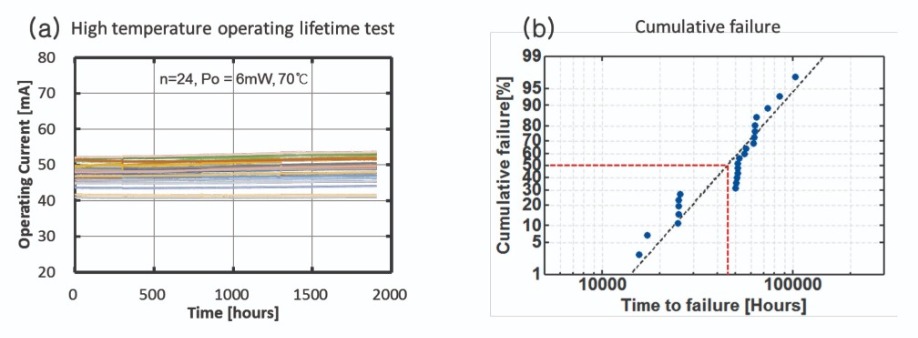

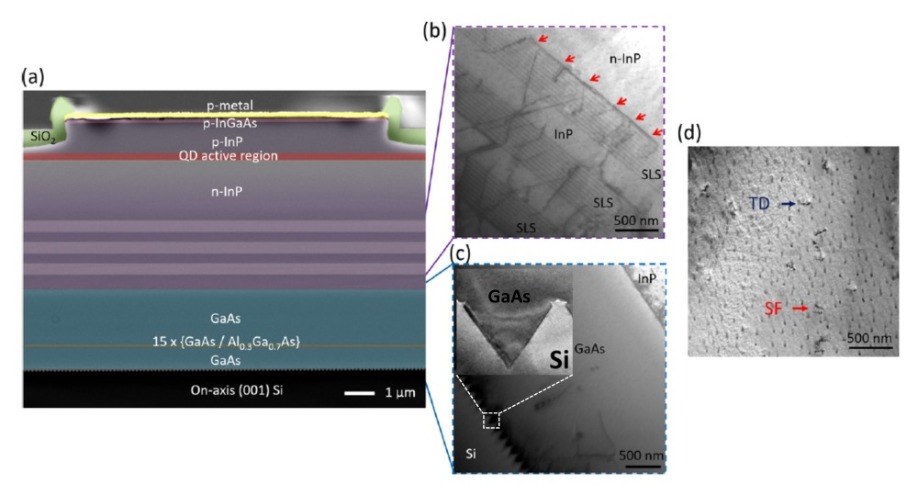

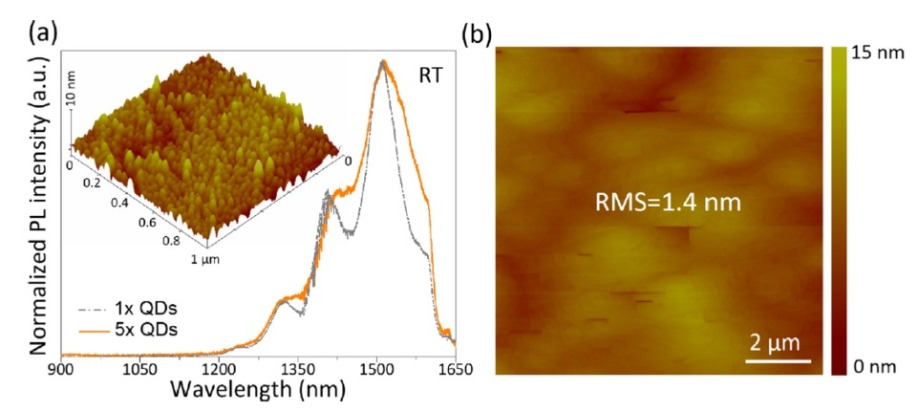

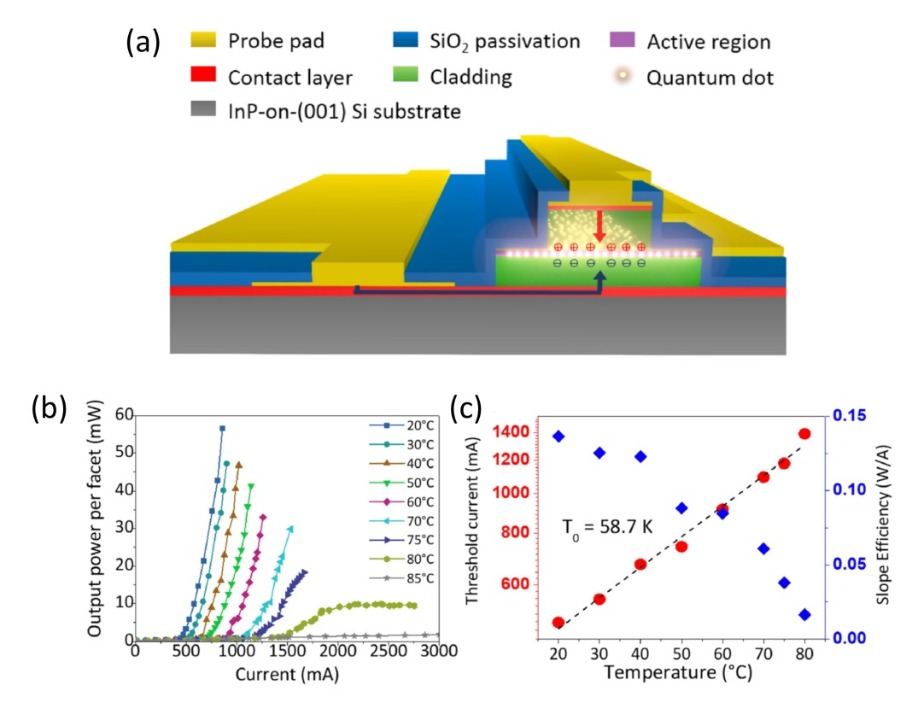

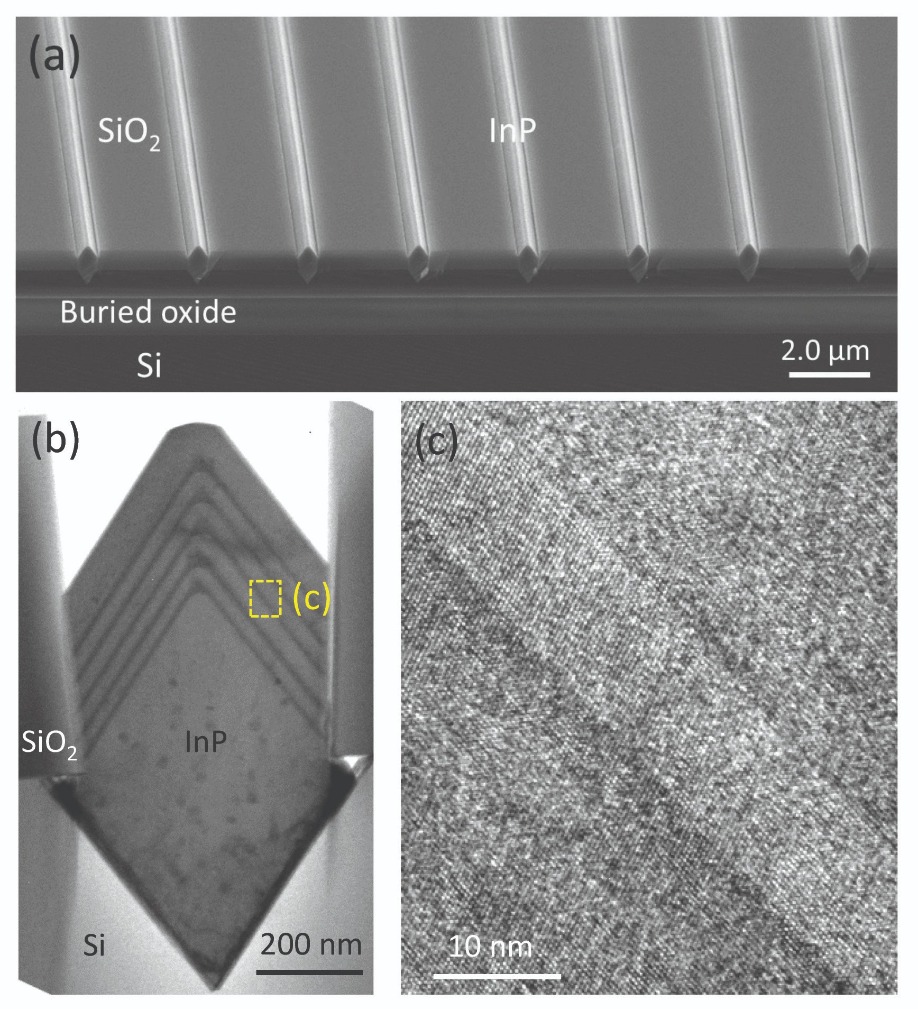

Introducing inter-chip optical interconnects could obliterate bandwidth and capacity limitations coming from today’s copper interconnects, which are hampered by impedance mismatches between the CPU and the dual-inline memory modules. This could create a form of DRAM with an optical interface, formed by integrating silicon-photonics-based optical transceivers in the DRAM on the bulk-silicon platform (see Figure 1).

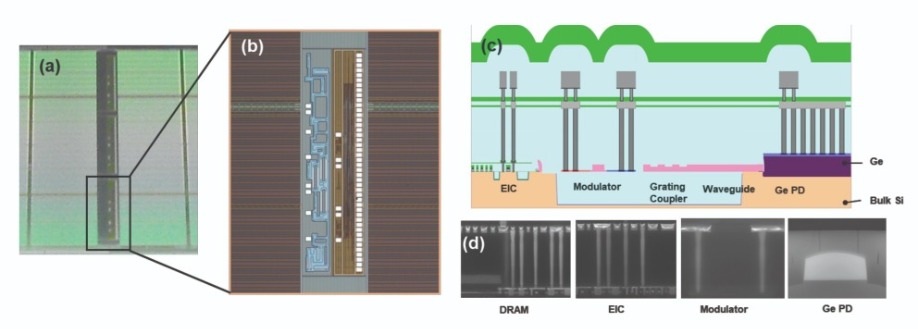

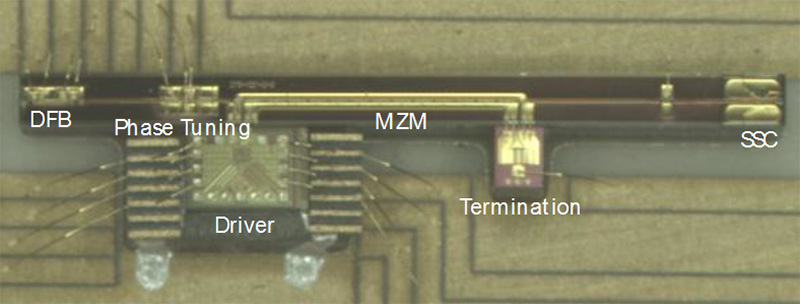

Figure 1. (a) Optical microscope image of a DRAM periphery section. (b) Optical microscope image of the electric-photonic IC. (c) Schematic of the electric-photonic IC vertical structure. (d) Scanning electron microscopy images of the DRAM, electric IC, modulator, and germanium photodiode. Note that this approach, outlined by Samsung in 2013, did not include the integration of lasers.

For this reason, at Samsung Advanced Institute of Technology, we are pursuing photonic IC technology on bulk silicon. Our breakthrough is the development of integrated lasers, implemented with a direct bonding process on the bulk-silicon platform. Our success provides a small but significant step towards the integration of photonic functions into legacy high-volume products, and it could contribute to mainstream semiconductor product evolution.

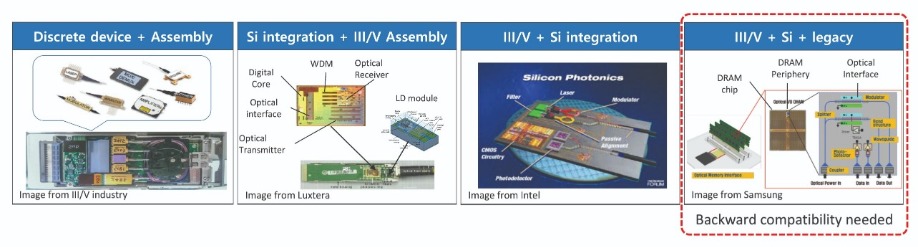

It makes sense for some smaller companies to develop their photonic technology on SOI, because the size of the emerging market for their technology is large enough for them. But for those of us that are players in the major semiconductor industry, which is already mass-producing electric IC products, the focus tends to be on the electric-photonic ICs. It is this technology that could support the electrical IC market of the future (see Figure 2).

Figure 2. The photonics industry is pursuing several different approaches to unite III-V and silicon technologies. For the last stage of the integration with legacy technologies, photonics integration needs backward compatibility with the legacy platform.

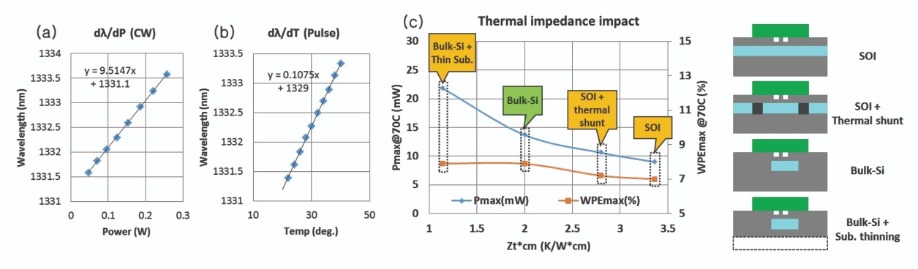

On the bulk silicon platform, developing the integrated laser is the biggest challenge. This building block, like all photonic devices on bulk silicon, suffers from a relatively high optical loss compared with the SOI platform. However, bulk silicon also has its upsides, including a lower cost and a superior heat dissipation that improves laser performance. It is these merits that give the implementation of electric-photonic ICs so much promise.

SOI versus bulk silicon

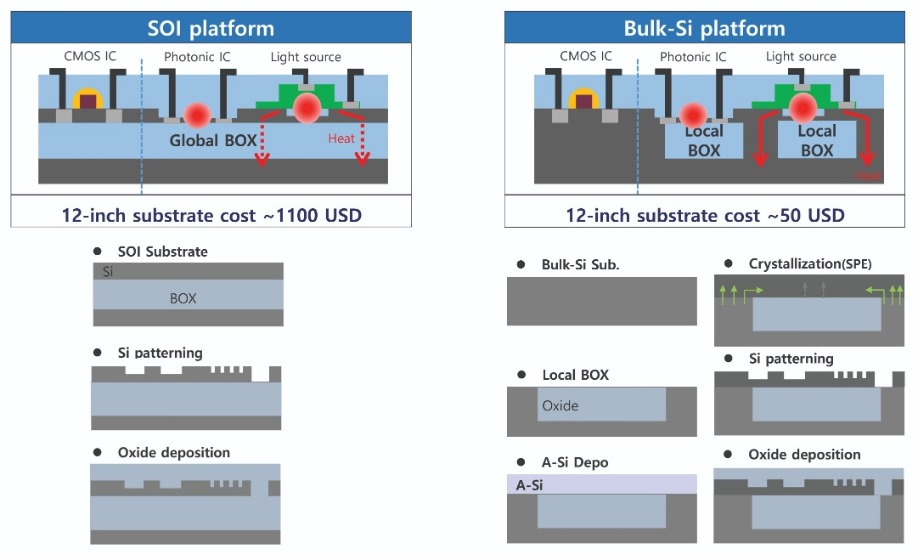

Despite a cost that is an order of magnitude higher than that of bulk silicon, SOI substrates are firmly established as the mainstream platform for silicon photonics, due to their ease of fabrication, and the low optical loss of the optical waveguides. At the heart of this technology is a global intermediary layer called a buried oxide. It sits beneath the thin crystalline silicon layer, where it creates a low-loss optical waveguide, by surrounding the high-index crystalline silicon core with a low-index oxide cladding. The downside of this architecture, as mentioned before, is its heat dissipation – the thermal conductivity is two orders of magnitude lower than that of silicon.

As this bulk-silicon platform is far lower in cost, and is currently used in most high-volume IC products, it is likely to be used in future electric-photonic ICs. With this platform, it is possible to add a buried oxide locally, under just the optical waveguide. This can impede light leakage, as well as increasing heat dissipation to the substrate, a move that prevents a plummet in the performance of temperature-sensitive devices.

Figure 3. Despite its high-cost substrate, the SOI platform has been dominant in the photonics industry. Merits of the bulk-silicon platform include its low-cost substrate, and its attractiveness for forming electric-photonic ICs. A noteworthy difference between the two architectures is that the SOI platform features a global buried oxide (BOX), while the bulk-silicon platform employs a local BOX.

Integrating III-Vs with silicon

As silicon lasers are still in their infancy, the lasers that are deployed in silicon photonics have to be made from III-Vs. The goal is to ensure low-cost coupling between the III-V laser and the silicon chip. Many solutions have been proposed, ranging from packaging-level assembly to process-level integration. With the assembly approach, the challenge is to realise high-precision optical alignment at low cost, while integration is held back by the substantial investment required to set up integrated processes for handling heterogeneous materials.

Once again, the approach that is adopted is dictated by the size of the industry. If it is small, the preference is on assembly, which provides a swift response to the emerging market; but if a company is operating in the major semiconductor industry, its interest lies in integration, with greater focus on high-volume manufacturing. Turning to integration avoids unacceptable increases in packaging costs, which are forbidden in the major semiconductor industry.

The bonding process is a popular short-term approach to integrating III-Vs and silicon. It overcomes the difference in the lattice constants of heterogeneous materials. Epitaxial layers of III-Vs are grown on a native substrate, before this epiwafer is flip-chip bonded to a silicon substrate that features pre-patterned silicon photonics structures. After the bond has been strengthened with a heat and pressure process, integrated lasers are formed using photolithography and III-V processing. The accuracy provided by lithography eliminates additional alignment.

Unfortunately, the scale and the maturity of silicon and III-V processes are very different. Consequently, integrating them is hampered by various technical and business issues, which may only be addressed with engagement of the overall semiconductor industry.

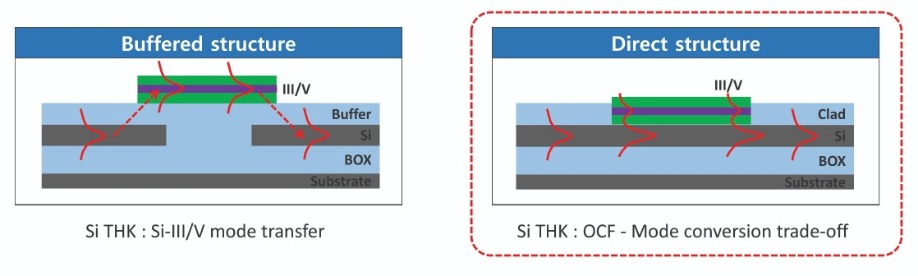

When pursuing this approach to integration, the first hurdle is to develop a good enough bonding process. Options include buffered bonding and direct bonding (see Figure 4). The former has fewer challenges, but the later delivers a simple silicon-to-III-V connection with diminished wavelength dependency.

Figure 4. The two main options for bonding are buffered bonding and direct bonding. The buffered structure takes full advantage of the traditional III-V active design and focuses on the smooth laser-waveguide mode transfer. The direct structure relies on an active design that depends on the III-Vs and silicon, and is capable of realising smooth laser-waveguide mode conversion. The thickness of the silicon plays an important role in mode transfer or mode conversion.

Building lasers on bulk silicon

With the bulk-silicon platform, a crystallized silicon layer must be formed on top of the local buried oxide. We do this with our proprietary solid phase epitaxy process. Essentially, this is a form of mild thermal annealing that turns amorphous silicon to crystalized silicon that mirrors the crystalline seed of the substrate. The crystallinity of the substrate propagates upwards in the regions directly contacting the amorphous layer, and propagates sideways over the local buried oxide.

Note that for the silicon at the centre of the local buried oxide, crystallization propagates from both sides – and when they collide, the result is poor crystallinity, known as coalescence. To prevent this poor crystal quality from impairing the performance of the optical waveguide, its location deliberately avoids the coalescence regions.

Putting aside for one moment the use of a local buried oxide and the offset location of the optical waveguide, we employ a process and structure that are similar to the SOI platform. However, our approach offers some advantages over this in terms of flexibility, as we can use arbitrary thicknesses for the silicon layers, the buried oxide, and the polysilicon reflective layers.

The most common method for getting the output of a discrete laser into a waveguide is butt-coupling. This is accomplished by aligning the laser and the waveguide on the same optical axis. In this configuration, the optical mode is positioned at the centre of the laser active region to maximise efficiency.