When I first heard of using CPV to power satellites, I thought it rather odd. But now, having learnt more about it, I’m starting to come around to the idea.

Up in space, this technology would take the form of modules incorporating from small cells and lenses. Modules would be pointed at the sun with high accuracy, just like the panels on the satellites of today.

Due to the high costs of getting anything into orbit – launch costs are around $10,000 per kilogram – key figures of merit for generating power in space are watts-per-kilogram and

watts-per-cubic metre.

Judged in those terms, CPV has great potential. Moving from flat panels to high concentration delivers a significant boost in efficiency, and by using lens with a focal length of just a few millimetres, the modules can be incredibly thin. So thin, in fact, that they can be drop-in replacements for conventional satellite panels.

Additional advantages of this class of module are a very high radiation tolerance, thanks to shielding from a glass lens array; and a reduced risk of arcing between cells, because these devices are spaced far apart.

Putting this concept to the test is a team from George Washington University, the US Naval Research Labs, Veeco, Northwestern University, MIT and X-Celeprint. This collaboration is developing modules that feature an array of small lenses, positioned above five-junction cells formed via the heterogeneous integration of triple-junction GaAs-based cells with dual-junction, InP-based cells. The modules can also capture diffuse light, thanks to the inclusion of a bifacial crystalline solar panel (see Sending CPV into space on p.36 for details).

Commercial success with this technology could be a double-edged sword for our industry. By increasing the bang-per-buck of solar power, it could lead to the launch of more satellites; but the III-V content on each one would be far, far lower.

The flip-side, however, could be growth in the CPV industry. Ultimately, this technology could then have more success back on earth.

It is well known that CPV failed to deliver its commercial promise in sunny climes, due to plummeting prices for silicon and the credit crunch. But the question marks surrounding its long-term reliability can now largely be dismissed, thanks to the efforts over the last decade at ISFOC (see Putting CPV to the test on p.28). So, as the levelised cost-of-energy falls, could CPV be poised to make a comeback?

The materials and optoelectronics firm II-VI and the optical communications company Finisar have entered into a merger agreement under which II-VI will acquire Finisar in a cash and stock transaction with an equity value of approximately $3.2 billion. I-VI and Finisar will employ over 24,000 associates in 70 locations worldwide upon closing the transaction.

The combination of II-VI and Finisar brings together their extensive capabilities in photonics and compound semiconductors to serve a number of fast growing markets including communications, consumer electronics, military, industrial processing lasers, automotive semiconductor equipment and life sciences.

The joint portfolio includes GaAs, InP, SiC, GaN and diamond technologies together with optoelectronic, optical and integrated circuit device design expertise and related intellectual property. This has the potential to unlock access to larger markets in RF devices for next-generation wireless and military applications, as well as power electronics for electric cars and green energy.

The combined company also has a full line and scalable supply of high performance datacom transceivers, products based on coherent transmission technology and ROADM solutions. It will market products into next-generation undersea, long-haul and metro networks, hyperscale datacentres and in 5G optical infrastructure.

There is also huge potential in 3D sensing and LiDAR based on their optoelectronics expertise in GaAs and InP compound semiconductor laser design platforms, together with one of the world's largest 6-inch vertically integrated epitaxial growth and device fabrication manufacturing platforms.

"Disruptive megatrends driven by innovative uses of lasers and other engineered materials present huge growth opportunities for both of our companies," said Vincent D. Mattera, Jr., president and CEO, II-VI Incorporated. "In communications, materials processing, consumer electronics and automotive, we expect that the combination with Finisar will allow us to leverage our combined technology and intellectual property in InP, GaAs, SiC, GaN, SiP and diamond to achieve faster time to market, cost and scale. Together, we believe that we will be better strategically positioned to play a strong leadership role in the emerging markets of 5G, 3D sensing, cloud computing, electric and autonomous vehicles, and advanced microelectronics manufacturing."

Mattera continued: "We have long admired Finisar and have a great deal of regard for its founders and its talented global team. Our companies both have a long history of focusing on innovation, breakthrough solutions and competitive follow-through by manufacturing high quality products for our customers, and we look forward to welcoming Finisar to the II-VI family and further strengthening our competitive position in the industry."

"The combination of our state-of-the-art technology platforms, deep customer relationships, great assets and amazing talent will enhance our ability to hit market windows that won't stay open for long," said Michael Hurlston, Finisar's CEO. "This combination will accelerate our collective growth and will take advantage of the technology, products and manufacturing expertise that Finisar has uniquely developed over the course of its 30 year history."

Hurlston added, "We are extremely excited to combine Finisar with II-VI and together create a leader in photonics and compound semiconductors across all of the markets we serve. We are confident that the growth potential for the combined company is substantial, and we believe that our respective shareholders will be able to enjoy significant potential for value creation when the transaction is completed."

A UK and Netherlands consortium of semiconductor device specialists has been awarded a two year, £1.2Million project to develop next generation photodetector solutions for ultra-high speed data-communications applications.

The Compound Semiconductor Centre (CSC) will deliver project MISCA (Monolithically Integrated Detector Solutions for Next Generation Communications Applications) in collaboration with Integrated Compound Semiconductors (ICS) Ltd of Manchester, and VTEC Lasers and Sensors of Eindhoven, The Netherlands.

Project lead, Wyn Meredith, director of CSC, commented: "The project aims to drive a radical improvement in component performance via advances in semiconductor materials integration and will result in a new European source of high performance detector products for fibre optic data-communications applications."

Mohamed Missous, founder and CEO of ICS said: "The rapid growth of the high speed optical transceiver market is an exciting opportunity for ICS as the demands of the 100G/200G/400G optical transmission markets require a deep understanding of RF component design to complement high quality optoelectronic device manufacture."

Jan Mink, CEO of VTEC added: "The Eurostars programme is specifically aimed at enabling agile SMEs to collaborate across Europe, and gives VTEC a great opportunity to collaborate with like-minded companies in the UK to extend our value chain. We see great potential in using semiconductor component integration to enable a new class of low power consumption, high performance detector products."

After a relatively flat year in 2016, revenue in the RF GaAs device market grew by more than 7 percent in 2017. While a wide variety of commercial and defence applications use GaAs devices, the wireless market continues to be the dominant user of this technology.

Mobile handsets will continue to define the revenue trajectory, but emerging 5G network deployments will contribute to future growth. The Strategy Analytics Advanced Semiconductor Applications (ASA) service report, 'RF GaAs Device Industry Forecast: 2017 - 2022' forecasts that RF GaAs revenues will push past the $9 billion milestone by the end of the forecast timeframe.

The Strategy Analytics Advanced Semiconductor Applications (ASA) service report, "RF GaAs Device Industry Forecast: 2017 - 2022," forecasts that RF GaAs revenues will push past the $9 billion milestone by the end of the forecast timeframe.

"Despite the dominance of the wireless segment, the RF GaAs market has been notable for the breadth of applications using the technology," noted Eric Higham, service director, Advanced Semiconductor Applications (ASA) service. "However, GaAs devices are facing challenges from other technologies and they are being commoditised in many of these applications. Future growth is going to depend heavily on LTE and emerging 5G networks."

"The situation for RF GaAs growth in the defense market is different," observed Asif Anwar, director of the Advanced Defence Systems (ADS) service. "New defence platforms and major upgrades are reaching the production phase and while the radar segment will remain the dominant application, all the defence segments will experience growth."3-5 Power Electronics, GmbH (35PE), an emerging power semiconductor technology innovator, has announced that it has secured new financing from the Sturm Family Office (SFO) of Bad-Mergentheim in Germany.

35PE has pioneered a first-of-a-kind process to deposit thick GaAs layers on top of GaAs substrates to produce high-voltage/high-current power semiconductors. The process aims to produce superior power devices at a lower manufacturing cost than devices built with silicon or SiC. Near-term applications include industrial motor drives, uninterruptible power supplies, and renewable energy products, such as wireless chargers for solar and wind inverters. Future applications include electric vehicles, robotics and 5G technologies.

35PE was founded in late 2015 to optimise GaAs technology to enable power devices. Led by a team of semiconductor technology and global business executives, the company has raised 5.3 million euro (US$6.10 million) to date. This includes funds previously secured from Shanghai-based SINO Alliance Investment Ltd. The new funds will be used to prepare 35PE's operations for product commercialisation which is planned for the second half of 2019, and to forge partnerships with established leaders to help speed the company's GaAs devices to market.

Samples of the company's GaAs diodes have been submitted for testing to power module makers in Europe and China. Applications include battery charging, welding and industrial heating.

GaAs technology has been used for decades to produce low-voltage/high-frequency devices. Now, the industry is leveraging the technology to build compact high-power semiconductor devices because of its inherent advantages over silicon, SiC, GaN, and other materials. Devices based on GaAs technology deliver higher energy savings, superior performance and greater reliability than those based on silicon.

For instance, when compared to a conventional SiC Schottky diode in a 3.3 kW wireless charging system, a GaAs-based device was shown to consume nearly 20 percent less power. What's more, GaAs-based power modules and systems can be as much as 50 percent smaller and lighter than the silicon alternative. Also, when compared to devices fabricated with wide-band gap (WBG), SiC and GaN materials, GaAs-based devices are far less costly to manufacture, while demonstrating equal, and often better performance advantages.

35PE's vision was to stretch the capabilities of GaAs technology and simultaneously improve the manufacturing economics. Thick GaAs layers are imperative for the production of high-power devices (>600 - 1700V and up to 100-150A). The company is the first in the industry to pioneer deposition technologies to produce high-power GaAs devices in high volume.

“We are thrilled to receive the new funding from SFO,” said 35PE's Chief Executive Officer, Dr. Gerhard Bolenz. “While we've laid the foundation to deliver a unique enabling technology solution to the power electronics industry, the new funding will help us build a global business. Most importantly, with growing customer interest in our technology, we can size our infrastructure for speedy response and service. We're grateful for SFO's support, and thankful to our existing investor who has championed our journey so far.”

SFO statement: “SFO is pleased to support 35PE with this new financing. We believe that the technology is clever, differentiated and enabling, with real potential to transform the power electronics industry. With nearly 90 years of collective semiconductor experience, the 35PE team has achieved critical technology milestones by executing with focus and discipline, and using their resources wisely.

At its headquarters in Dresden's Silicon Saxony region, 35PE has established a lean model to develop, produce and distribute high-voltage GaAs wafers and related semiconductor devices for power electronics. Multiple patents have been filed worldwide and one has already been granted. In addition, the company has established select distribution networks in Asia to create an efficient feedback loop between the company and end-users. In parallel, the company is pursuing partnerships with strategic investors and global manufacturers to execute more speedily on its technology roadmap and accelerate its market entry.

Infineon has acquired Siltectra, a Dresden-based start-up that has developed an innovative technology called Cold Split to process crystal material efficiently and with minimal loss of material. A purchase price of €124 million was agreed on with the venture capital investor MIG Fonds, the main shareholder.

Infineon will use the Cold Split technology to split SiC wafers and double the number of chips per wafer.

"This acquisition will help us expand our excellent portfolio with the new material SiC as well. Our system understanding and our unique know how on thin wafer technology will be ideally complemented by the Cold Split technology and the innovative capacity of Siltectra," said Reinhard Ploss, CEO of Infineon. "Thanks to the Cold Split technology, the higher number of SiC wafers will make the ramp-up of our SiC products much easier, especially regarding further expansion of renewable energies and the increasing adaptation of SiC for use in the drive train of electrical vehicles."

Jan Richter, CTO of Siltectra: "We are glad to become part of the team of the global market leader in power semiconductors. Having shown that the Cold Split technology can be used at Infineon in principle, we will now work together to transfer it to volume production."

Michael Motschmann, general partner of MIG Fonds' administrator MIG AG, said: "Since we invested in Siltectra more than eight years ago, we have always believed in the Cold Split technology and the great team. We are very pleased that we found Infineon as a buyer who fits perfectly technologically as well as culturally to the company. Furthermore, it makes us proud that we helped to strengthen Germany's economic competitiveness by our investment."

Siltectra was founded in 2010 and has been growing an IP portfolio with more than 50 patent families. The start-up developed a technology for splitting crystalline materials with minimal loss of material compared to common sawing technologies. This technology can also be applied with the semiconductor material SiC, for which rapidly rising demand is expected in the coming years. SiC products are already used today in very efficient and compact solar inverters. In the future, SiC will play a more and more important role in electro-mobility. The Cold Split technology will be industrialised at the existing Siltectra site in Dresden and at the Infineon site in Villach, Austria. The transfer to volume production is expected to be completed within the next five years.

Rohm recently announced the development of a 1700V/250A rated SiC power module that provides the industry's highest level of reliability optimised for outdoor power generation systems, such as inverters for solar power and converters for industrial high-power supplies.

In recent years, due to its energy-saving benefits, SiC is seeing greater adoption in 1200V applications such as electric vehicles and industrial equipment. The trend towards higher power density has resulted in higher system voltages, increasing the demand for 1700V products. However, it has been difficult to achieve reliability, and so IGBTs are typically preferred for 1700V applications.

In response, Rohm was able to reach high reliability at 1700V, while maintaining the energy-saving performance of its popular 1200V products, achieving the first successful commercialisation of 1700V rated SiC power modules. The BSM250D17P2E004 uses new construction methods and coating materials to prevent dielectric breakdown and suppress increases in leakage current. As a result, high reliability is achieved that prevents dielectric breakdown even after 1,000 hours under high temperature high humidity bias testing (HV-H3TRB). This ensures high 1700V withstand voltage even under severe temperature and humidity environments.

By incorporating Rohm's SiC MOSFETs and SiC Schottky barrier diodes into the same module and optimising the internal structure, it has been possible to reduce ON resistance by 10 percent over other SiC products in its class. This translates to improved energy savings in any application.

Going forward, Rohm says it will continue to expand its lineup to ensure worry-free use by customers and work to increase demand by offering evaluation boards that allow easy testing and verification of the SiC modules.

From end-to-end and in just five years, the Compound Semiconductor Applications Catapult intends to have transformed the UK supply chain. Chief Executive, Stephen Doran, tells Rebecca Pool, how this will be done.

In August this year, the South Wales-based Compound Semiconductor Applications Catapult launched with an ambitious remit to accelerate UK economic growth in compound semiconductor-related industries.

Having received a hefty £51 million in government funds, the centre already employs some 23 staff and intends to soon create around 100 jobs internally, including engineering positions.

As the Catapult chief executive, Stephen Doran, puts it: “We are open for business, hiring and ramping up business and want to make a real difference to the UK supply chain... come work and collaborate with us and we can grow UK industry.”

Ask Doran about future Catapult plans and he is quick to point out the scale of the opportunity for UK-based compound semiconductor companies.

Analysts have estimated the global market for compound semiconductors is set to grow from a 2016 figure of $66 billion to more than $300 billion come 2030; three times the growth rate of silicon.

What’s more, recent analysis from Doran and colleagues indicates that in 2017, the global market had already increased to $74 billion.

Given these rapidly rising numbers, the impact of even a few percent increase in market share could be profound for any nation.

“The UK currently has around 9 percent of this market share and we need to maintain this share,” says Doran. “But if we can help the UK to increase this share by even just one, two or three percent, this would make a significant difference from an economic perspective.”

According to Doran, collaboration amongst existing UK companies is going to be critical to growing to market share. Catapult figures indicate that the UK already has more than 100 companies actively working with compound semiconductor devices.

Meanwhile, some 5,000 UK businesses – of which 90 percent are SMEs – are designing and making electronic components, devices and systems.

For its part, the Catapult has already been in contact with hundreds of businesses – including Anvil Semiconductors, Microsemi and IXYS UK Westcode – to develop its strategy. And the centre intends to work with more than 1000 business and help to create 1000 jobs come 2023.

But right now, a coherent supply chain does not exist. As the chief executive points out: “We have talked with SMEs and sometimes these companies ask us, ‘how can you help us to gain access to the tier one players’. Yet at the same time, tier one players say, ‘where is the supply chain across the UK’.”

To help to address this disconnect, the CSA Catapult is in the process of setting up an Innovation Centre, scheduled to open at the end of March 2019. “This centre is designed to be open and collaborative, so companies can overcome this barrier and get together,” points out Doran.

Crucially, the centre will also house a design studio, as well as laboratories and test facilities supported by simulation and modelling tools to get compound semiconductor development out of the lab and into industry.

“From our discussions, SMEs see access to expensive capital as well as the expertise to operate the capital as a key industrial barrier; the Innovation Centre will help here,” says Doran.

“Today industry is well advised in, for example, silicon modelling tools, but life becomes difficult in mixed-signal [devices] and even more difficult when you bring in compound semiconductors; so we are looking to make investments to improve models so more designs can come through.”

The Catapult is also intent on designing and manufacturing Evaluation Modules – using UK-sourced semiconductors where possible – to help companies prototype systems more quickly and cheaply.

The first modules will be for power electronics, radio frequency and microwave, and photonic applications. And as Doran highlights: “There’s a cost, cycle time and labour element to developing these, and it will easily cost half-a-million pounds to develop an evaluation module.”

“But we are in the process of deciding the first modules with industry now, as we want to get [devices] to the market fast,” he adds. “We expect to deliver six in the next two years.”

In addition to the Innovation Centre and Evaluation Modules, Challenge Programmes also form a critical, third arm of the Catapult’s strategy. Due to be announced within weeks, these programmes will be set up to identify how compound semiconductors can address global challenges and help SMEs to supply products to large companies with access to global markets.

As part of this, the Catapult will be assessing if industry needs a particular compound semiconductor supply chain, and has already identified the need for a scalable supply chain in the production of silicon carbide. “This doesn’t exist today as an open foundry,” says Doran. “If companies want to buy silicon carbide they go elsewhere or create that capability themselves.”

“But if we create a silicon carbide supply chain in the UK, and from there develop evaluation modules that go straight into industry, this would be a huge help... we would have a supply chain right on the doorstep for UK industry,” he adds.

Next moves

So as the Catapult makes its final decisions on Evaluation Modules and Challenge Programmes, bringing companies together to establish a solid UK compound semiconductor supply chain will no doubt remain a key theme. Doran is keen to highlight the successes of wafer producer, IQE, but also points out the potential to grow the supply chain from here.

“IQE are at the early part of the supply chain, yet more value lies at the consumer end of the chain,” he says. “So as we work our way along that supply chain, the more value we can embed in the UK, the better the overall economic impact for us.”

Indeed, only weeks ago, the Catapult announced a collaboration with the University of Bristol, to find out the best way to get the university’s cutting-edge thermal wafer mapping tool, Thermap, to the businesses that need to characterise wafers.

“The UK has so much core capability but we are not so good at collaborating,” he says. “We want to make sure companies in the UK understand the potential of what is in the UK... this ability to link one company with another is going to be extremely powerful.”

With rapidly rising revenues, industry can expect more growth and a ‘dream MBE’ system from Riber, reports Rebecca Pool.

For France-based semiconductor equipment business, Riber, 2018 has so far been very productive. Aided by buoyant market conditions, Riber’s revenue has grown 42 percent year-on-year for the first nine months of 2018, largely driven by sales of its MBE systems almost tripling.

And with analysts tipping the MBE system market to mushroom in coming years, Riber’s growth looks set to continue.

“Riber has always invested around 10 percent of its sales into research and development and we also have had a lot of collaboration with many European laboratories,” says Riber chief executive, Philippe Ley. “While research markets have been steady for many years, we are now seeing a lot of growth in production markets.”

“This is the era of IT and telecommunications, and MBE can produce very efficient devices for these markets,” he adds. “So for me, it is now all about improving existing equipment and developing new systems.”

Ley joined Riber in June this year, following an eight year stint as production and operations director as well as management board member. Tasked with driving company development as the MBE market grows, much has happened since he took the position of chief executive.

In July this year, Riber opened its 100 percent owned subsidiary, Riber Semiconductor Technology Shanghai, to strengthen the company’s presence across China.

As Ley points out: “Customers in China wanted better service, maintenance, help and after-sales service so this supports them, and provides the same service that you would get in Europe.”

Indeed, Riber already has 21 MBE customers in China with an installed base of 48 machines. Six of these are production systems, giving Riber the largest installed MBE base in China and a market share of more than 75 percent.

What’s more, in the same month, China-based laser systems developer, Acken Optoelectronics, ordered a MBE 6000 multi-wafer production system from Riber. And the company recently revealed a further sale to a ‘new customer from Asia’, to manufacture optoelectronic systems for fibre-optic interconnection markets.

Rising sales come at a time when several massive government projects are under negotiation to roll out large-scale fibre-to-the-home and 5G networks to serve Chinese markets.

“We know that Chinese customers would like to have more MBE systems in China so they can make more of their own electronic components, rather than buying them abroad,” says Ley. “People want fibre-to-the-home and 5G, and companies wish to be more independent... so yes, they will need more machines and our new subsidiary will be important.”

Looking beyond China, MBE system sales worldwide show an incredible 193 percent growth in the last nine months, compared with the same period in 2017. And Riber’s MBE systems order book is also looking very healthy, with orders increasing by a hefty 120 percent to €22.2 million in the last year.

According to the company, twelve systems – comprising seven production and five research machines – are scheduled for delivery between 2018 and 2019. In contrast, four production and two research systems were delivered in 2017.

Given this solid schedule, Riber predicts full-year revenues of Ä35 million for 2018 and at least 15 percent year-on-year growth. And Ley is confident the company will hit its targets, saying: “We have good prospects and a good plan and expect to see steady growth over the next three years.”

Dream machine

So what next for Riber? Right now, the company is intent on delivering what Ley calls its ‘dream MBE’ by 2021. As he explains, the next-generation MBE system will be ‘entirely user-friendly’ with a higher level of integration of in-situ characterisation tools, relative to current systems. Such tools will include optical-based flux monitors and pyrometers, and will provide the necessary deposition data to optimise quality control during epitaxy.

“You can sub-contract many of these tools, but we want to have an intelligent machine that can better use the system information to produce higher quality layers and better wafers,” says Ley. “It needs to be easy to use and have a high efficiency... we have many new customers around the world, and for sure in China, but not all have enough MBE knowledge.”

“Many customers do not want to make many tunings themselves, so such a system would really increase productivity,” he adds. “Our target is to develop a first system next year and have the final machine ready to be sold in 2021.”

But what about competition from MOCVD systems, perceived by many to be more user-friendly? Ley remains unfazed and as Riber chairman, Michel Picault, tells Compound Semiconductor: “MOCVD is a good tool for mass production while MBE is better for higher-end performance devices.”

“This is why we are seeing rising demand and potentially a very large market for these devices, including laser diodes and VCSELs, in 5G and fibre optic networks, and many more applications,” he adds.

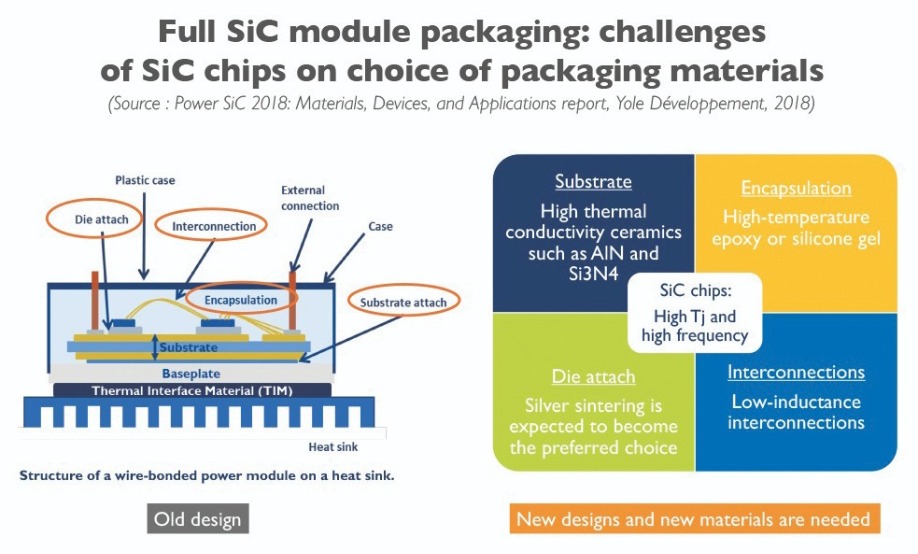

As more and more wide bandgap semiconductors reach electric vehicle markets, industry can expect rapid power module package development, reports Rebecca Pool.

Earlier this year, Yole Développment analyst, Hong Lin, revealed how the in-flux of wide bandgap semiconductors to electric and hybrid electric vehicle markets is driving the development of new power-module packages.

As she tells Compound Semiconductor, more than twenty automotive companies are already using SiC Schottky barrier diodes or MOSFETs in DC-DC converters, the main inverter and onboard chargers, fuelling a 29 percent compound annual growth rate from 2017 to 2023.

What’s more, in the short-term, nearly all automotive manufacturers have programmes to implement SiC into the main inverter.

However, all good power devices need a good package to perform, and without a doubt, packaging has long been a bottleneck for wide bandgap device applications.

The packaging of SiC power devices has relied heavily on the same wire bonding approach used in silicon MOSFETs and IGBTs, largely because of its ease-of-use and low production costs.

But while this suits the tens-of-kilohertz switching frequencies demonstrated by silicon devices, hit the much higher megahertz speeds of SiC systems and parasitic inductances pose a problem.

Parasitic inductance in the power module induces high-voltage overshoot and ringing on switching devices, which then increases the device switching loss and EMI emission from the modules.

Couple this with the fact that the operating temperatures of SiC device packages now reach a scorching 225 °C, and one understands why the likes of Wolfspeed, Rohm, Infineon and GeneSiC have been busy pioneering new packaging structures to better handle the extreme switching speeds and temperatures.

At the same time, innovations, such as the use of copper connections and silver sintering joints instead of aluminium wire bonds and solder joints, have also emerged.

“Packaging-induced noise has a huge impact on device performance,” highlights Lin. “And so researchers have been working on reducing the inductance of the package, with many companies developing different types of packaging for this.”

The recent SiC-based inverter, developed by STMicroelectronics for Tesla’s all-electric Model 3, is a shining example of such innovation.

The inverter comprises 24 power modules, assembled on a custom-design ‘pin-fin’ heatsink. Each module contains two SiC MOSFETs with a novel die attach and connected directly onto the terminal with copper clips. Meanwhile a copper baseplate provides thermal dissipation.

“Tesla is one example, but almost all OEMs for car manufacturers have been looking at SiC technologies here, and each car company will adopt SiC at its own pace,” says Lin. “Mitsubishi Electric is another important player here, and has been providing lots of innovation in automotive as well as rail markets.”

Pick and choose

Still, automotive manufacturers remain technology-agnostic, keen to implement cost-effective, reliable systems, be they based on silicon or SiC.

“All silicon power device suppliers have a silicon carbide programme and are also looking at a gallium nitride programme,” comments Lin. “And there is not a packaging technology that we can say is only used in compound semiconductor-based systems.”

“These traditional silicon power device manufacturers also have a lot advantages over newer start-ups,” she adds. “For example, they understand packaging technologies very well and have a broad knowledge of applications and what a design needs... and of course they can leverage their internal capacity to take advantage of market growth.”

Indeed, looking to the future, Yole Developpment has forecast that the entire power module market will exceed $5.5 billion come 2023. “The industry is in an emerging stage right now with many companies proposing many different types of packaging,” says Lin. “The type of package also depends on its applications, and we can expect to see more and more customer designs being delivered to industry in the next few years.”

Wide bandgap semiconductors demand new package designs.

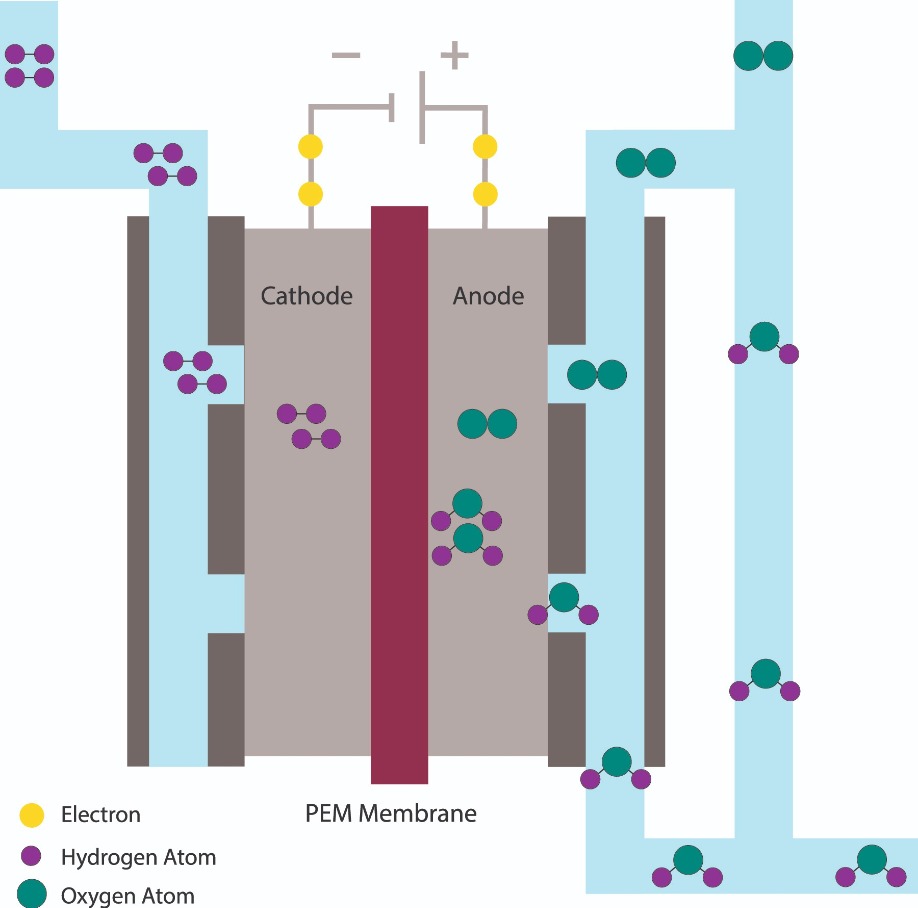

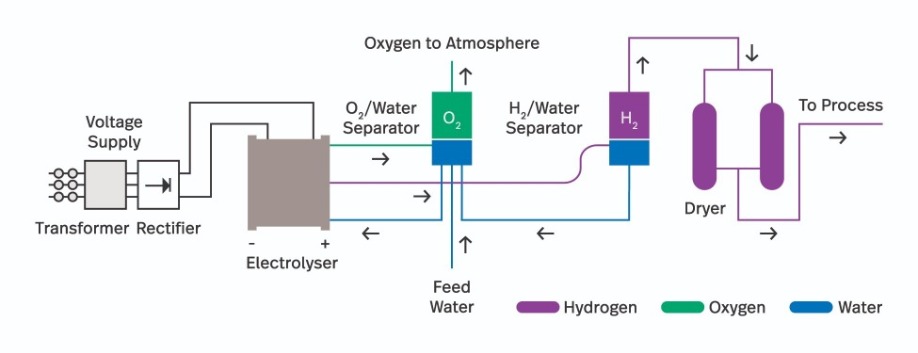

For low risk, low-cost production of high-purity hydrogen, makers of compound semiconductor epiwafers should install electrolysers based on proton exchange membrane technology

BY TOM SKOCZYLAS FROM NEL HYDROGEN

An essential process in the manufacture of compound semiconductor chips is the growth of a stack of epitaxial layers, which are subsequently processed into devices. Most often the growth of this heterostructure is carried out by MOCVD, a process that involves the decomposition of two or more types of organic molecule on a heated substrate to yield a thin film.

In this growth process, two key ingredients are metal-organics and the gases containing group V elements, such as arsine and phosphine – it is the decomposition of these sources and their subsequent reactions that produce the compound semiconductor epilayers. However, these are not the only materials with a critical role to play. There is also hydrogen, which is widely used in the production of devices based on arsenides and phosphides. This gas transports the metal organics, along with phosphine and arsine, from their containers to the growth chamber. Due to the rise in production of all forms of compound semiconductor chips, the demand for scalable, reliable, affordable, high-purity hydrogen is at an all-time high.

How pure is pure?

To ensure high-quality LEDs, VCSELs, transistors and the like, rigorous standards have been set for hydrogen purity. However, it is critical that this is assessed in a quantitative manner, rather than vague marketing terms. Different purity grades and terms are used by different suppliers, such as ultra-high purity and semiconductor grade – but they are just marketing nomenclature, and they fail to provide a quantitative description of the purity of the gas.

Makers of compound semiconductor devices will want to know the purity of hydrogen. It is often given in terms of the number of ‘nines’. For example, ‘five-nines’ would be used to describe hydrogen that is at least 99.999 percent pure. But that is not all that these chipmakers want to know. The nature of the impurity is also critical. It may be that the impurity is ‘destructive’ to the process, degrading process yield or impairing process control and leading to a cost increase in manufacturing. Or, worse still, impurities could result in device malfunction. That’s the threat with methane and CO, which may have to be completely avoided, or kept below well-determined limits.

Since the purity of hydrogen is so critical, it must be maintained up to the point of use. It is fruitless ensuring that the purchased hydrogen meets the level of purity for the process, and then compromising its integrity by transporting it to the facility through long-distance piping.

Delivery options

A pipeline is by no means the only option for delivering hydrogen. In fact, using a pipeline is rare, as it is only available when sites are near a large hydrogen production facility. More typical is delivery by truck. In that case, hydrogen either arrives in a compressed form in cylinders or high-pressure tubes; or for larger users, it is supplied as a liquid in a tank trailer, and offloaded into a site storage tank. There is also a third option, gaining in popularity: on-site generation using proton exchange membrane water electrolysers.

There are many challenges involved with delivered hydrogen, including specifying and maintaining purity. For instance, purity can be dependent on the method of production. Options for manufacturing hydrogen include methane or other hydrocarbon processing, salt brine electrolysis, and water electrolysis – and they can all introduce different impurities.

Once generated, all hydrogen is purified. How this is done is critical, depending on both what is removed and how this is accomplished. What are the risks to purity with this process?

Purity may be inconsistent, varying between batch deliveries. The cleanliness of the delivery vessels is beyond the customer’s control, as is the possibility of introducing contaminants every time a connection is made or broken on the supply side. Compromises to hydrogen purity can occur when filling up at the supplier’s facility, offloading at a previous stop or at the customer’s facility, or when changing out cylinders and tubes.

When deciding how to receive hydrogen, there are factors to consider that go beyond the integrity of purity. Delivery and offloading compressed gas or liquid hydrogen introduces site and personnel risk. There is also a safety risk associated with the moving, connecting and disconnecting of cylinders and tubes, and the transfer of liquid hydrogen from a tank trailer to a storage tank at the customer’s facility. All these tasks must be managed with strict discipline.

Many manufacturers of silicon wafer chip, semiconductor and MEMs use proton exchange membrane water electrolysers.

One drawback of having hydrogen delivered to a site is that its supply cannot be guaranteed. Deliveries can be delayed by a natural disaster, such as a storm or flood; by demand exceeding supply capabilities; and by labour strikes affecting the supplier’s plant or delivery methods. Whatever the reason, interruptions can wreak havoc. In the worst case scenario, chip making may have to stop, leading to the loss of key customers due to delays in shipments.

When hydrogen arrives on site, it needs to be stored with great care. It is a highly hazardous and flammable material, and it must be accommodated in tanks or cylinders that are compliant to codes and standards enforced locally and nationally.

In the US, storing of hydrogen must be undertaken in a way that meets precautions based on quantity and pressure, according to the NFPA2 Hydrogen Technologies Code, as well as codes prevalent in various states and municipalities. These codes may include EPA, NFPA, OSHA and frequently even more stringent local regulations.

A proton exchange membrane water electrolyser cell stack produces hydrogen by splitting deionized water into hydrogen and oxygen. Unlike hydrogen produced from fossil fuels and other methods, there are no other contaminants present that can enter the hydrogen stream.

To meet these requirements, hydrogen storage may have to be sited well away from other buildings, in order to separate tanks from sources of ignition, air intakes, wiring, pathways and building walls. This situation brings its own issues, such as the need for expensive piping, which could become prone to leaks. There may also be the need for special permits, depending on local safety standards, that insist that engineering details are provided to appropriate authorities.

It is also important to be aware of the magnitude of the hazard. Just 1 m3 of hydrogen gas has a chemical energy equivalent to 2.9 kg of TNT. So a typical portable cylinder tank, which holds about 6.9 m3 of hydrogen, has as much energy as 20 kg of TNT – a sobering thought when manoeuvring hydrogen tanks and cylinders on or off manifolds feeding a facility. Note that typical facilities may store between 100 m3 and 3,000 m3 of hydrogen, equating to 290 kg to 8,700 kg of TNT. And if hydrogen is stored in liquid form, the magnitude of its energy is far, far higher. The remote possibility of a hydrogen explosion may not just be a major concern for those that work at the facility – it can be a worry for those that live nearby, who may over-estimate the risks and react in ways that do not support local chip making.

When siting a hydrogen storage area, several criteria must be considered. As hydrogen is not odorized, unlike natural gas, sensors and alarms may be required to alert safety personnel in the case of a leak. Storage may also need to comply with maximum inventory limitations according to regulatory codes, and there may be requirements for fencing and signage of the storage area. Generally, the sterile area near hydrogen storage is unavailable for parking or other uses.

On-site generation

An increasing number of compound semiconductor chipmakers are avoiding issues associated with the over-the-road delivery and storage of hydrogen by switching to on-site generation of hydrogen, in the form of proton exchange membrane (PEM) water electrolysers.

A key benefit of this technology is that it eliminates risks associated with deliveries and the maintaining of a hydrogen supply – because there is zero inventory required. Eliminating a hydrogen inventory means that the regulations associated with bulk hydrogen storage no longer apply. With a hydrogen generator, the magnitude of any leak cannot exceed the hydrogen production rate. Thanks to this, there is no danger of a leak filling the surrounding area with hazardous levels of hydrogen. What’s more, all piping remains tight, as there is no need to remove, replace or refill tanks.

When considering purchasing a PEM water electrolyser for on-site hydrogen generation, one should make sure the system is designed in accordance with NFPA and OSHA regulations for indoor installation. This means that the hydrogen supply can be closer to the point of use, trimming the length of piping, and in turn minimizing the risk of leaks and contamination.

With appropriate drying, PEM water electrolysers can produce pressurized hydrogen with a purity of at least 99.9995 percent on a constant basis, due to the stoichiometry of the generation process. Using this approach, production avoids the introduction of contaminants associated with the manufacture and transport of hydrogen from other sources, such as petroleum-based raw materials. The technology

also eliminates variations in impurities from batch to batch, because electrolysers continually produce hydrogen from water. In addition, contamination issues arising from cylinder change-out and refilling are eliminated.

Reliability also benefits from the use of electrolysers. As hydrogen is made on-site and on-demand, the supply of this source is not disrupted by uncontrollable situations such as severe weather, traffic tie-ups, accidents, labour strikes at the

supplier or trucking facility, and shortages in the supply chain. The generators are fully automatic, so no personnel are required for 24/7 operation (dependability is proven in submarines, where PEM electrolyser cell stacks provide oxygen for life support). Since there are limited moving parts – primarily a circulation pump, a circulation fan and a few solenoid valves – these units require minimal maintenance.

PEM water electrolysers also have the upper hand in terms of cost control. The price for hydrogen delivered from an off-site source may fluctuate significantly, while the costs for hydrogen generated on-site with an electrolyser are relatively fixed, and limited to capital, electricity and preventive maintenance.

Another benefit of PEM water electrolysers is that they allow users to produce very pure hydrogen at a lower cost than alternatives, even at low usage rates. And if the user’s demand increases, there are options for increasing capacity. Depending on the model, units can be expanded by adding components to increase output capacity, or more machines can be installed to match the customer’s process needs.

PEM water electrolysers will transform the industry. Up until recently, larger fabs have had to store large quantities of hydrogen to meet their production requirements. Now, with the introduction of electrolysers that have a capacity of up 1 Nm3/hr to 4,000 Nm3/hr, a greater range of operations, from small start-ups and educational facilities to high-volume plants, are able to benefit from on-site hydrogen generation systems that are armed with the attributes of high purity, low risk, and low-cost.

The flow of hydrogen, oxygen and water in a proton exchange membrane water electrolyser.

When a university installs its reactor in a commercial foundry, there are benefits for students, research groups and the chipmaker

BY RICHARD HOGG FROM THE UNIVERSITY OF GLASGOW

When business is booming, manufacturers of compound semiconductor devices find it a challenge to recruit PhD graduates with experience in MOCVD growth. Expertise on this front is highly valued because the growth of high-quality epilayers using this technique is a key process in the production of LEDs, lasers, solar cells and transistors.

However, it is unlikely that these PhD graduates will hit the ground running when they start work in a III-V foundry. Their skills have been honed on small tools designed for growing material for research purposes, in labs run in a manner that are research focused, and so not aligned with best practice for high-volume production. These new recruits will only be at their most productive after being given a chance to acquire the skills to run a high-throughput MOCVD reactor, housed in a cleanroom with a strict set of operating guidelines in terms of quality, yield, and cost.

But it doesn’t have to take this long to get up to speed.

The solution is to adopt another way of working: site the university’s MOCVD tool in an independent, volume-producer of III-V compound semiconductors. That’s the approach we are pioneering at the University of Glasgow, with our reactor housed at CST Global’s manufacturing facility in Blantyre, on the outskirts of Glasgow.

This new facility is jointly managed by ourselves and CST. This approach to operating an MOCVD tool is not just of great benefit to the PhD students. It’s also a winner for the research group, the chipmaker and the local economy.

Our students benefit from working in a commercial setting, with an MOCVD tool operating in a cleanroom complying with ISO 9001:2015 quality, the highest environmental and safety standards, housed besides foundry services. In this environment, our PhD students are rubbing shoulders with experienced engineers on a day-to-day basis. They therefore pick up informed, industrial knowledge, benefiting their development and employability. This unique environment targets the production of work with both commercial value and academic excellence. In turn, this allows us to to recruit high-calibre PhD students, being attractive to those who prefer to work in a commercial environment whilst studying, as it can make them more employable than those who dedicate their time to more fundamental work.

Another great advantage of our new approach is that the novel semiconductor materials and devices developed during our electronics and photonics research projects can be taken seamlessly from the laboratory to commercial, volume production. That’s obviously not the case when similar developments occur in universities with more traditional ways of working. In those environments, efforts to commercialise technology often require a senior academic to launch a start-up. That takes a lot of time and effort – but they are not the only drawbacks.

A far bigger issue is the clear conflict of interest between the commercial and academic worlds. In a commercial setting, a company must ‘feed’ a reactor with R&D and manufacturing work to ensure profitability and achieve a return on investment. Success requires an overhead of strong sales, administration, production and marketing infrastructures, not to mention a customer base to sell to. And the more repetitive the work the better, as margins rise when a tool is optimised for volume production of familiar, repeatable products. This is the domain of efficient business.

By contrast, a university, which holds charitable status, cannot operate effectively in a commercial environment. A university may undertake research projects for commercial entities, but these can be less inclined to further knowledge and understanding; instead they major on the development of manufacturing processes and rapid pay-back. A commercial focus therefore often conflicts with the academic aims of the university, where the measure of excellence is research with a high global impact. It is this metric that drives the ratings of our schools; the recruitment of our students; and the level of funding from research organisations and investment from the university. The majority of academics are driven by creativity, and judge their success by various factors, such as the number of citations of their high-quality research papers. Business accolades and efficient production often mean little to them, making their very involvement in managing a spin-off business a possible distraction.

Further benefits of housing a university-owned MOCVD reactor in a commercial setting relate to health and safety and the cost of ownership. Running an MOCVD reactor requires the use of potentially toxic, explosive chemicals. They can be costly to source, have long lead times, and are a security issue. And their use requires infrastructure to ensure safe handling of gases and their abatement. When the MOCVD reactor is sited in a commercial setting, these issues are far easier to address. That’s partly because it is far more likely that there are staff with experience of handling environmental protection procedures and legislation. What’s more, a university campus is, more often than not, a poor choice to house such a reactor. In our case, The University of Glasgow is surrounded by suburban regions of Glasgow and traversed by several thousand people a day. Additionally, many of our buildings are accessed very easily by our students and visitors. An industrial setting is clearly a far better option!

What about the benefits for the company that has a university-owned MOCVD reactor within its facility? Well, in the case of CST, by collaborating with us on cutting-edge research projects, it can identify the very best PhD talent available for recruitment. Three highly employable PhD students are currently coming through this route.

In addition, CST Global uses the MOCVD reactor for its research projects, including university collaborations, and has an agreed percentage of the reactor’s capacity reserved for its own work. This allows their other growth tools to concentrate on volume production. The CST custom foundry setting, where many separate confidential projects are executed on a daily basis has been beneficial in teaching me new working methods. These allow the MOCVD tool to be included in both highly collaborative working with CST, but also the development of devices and processes with trade secrets being developed and maintained with other collaborators.

Benefits of this way of working even extend beyond those for PhD students, universities and chipmakers: it is good for the nation. In Scotland, by leveraging our academic and commercial infrastructures, we are creating jobs and contributing to the UK economy. This should help us to attract more great people to come to Scotland, furthering our already strong photonics and electronics industries.

Professor Hogg heads a group that is researching device physics and engineering, epitaxial processes and fabrication technologies. These efforts are helping to develop diverse applications for semiconductor devices.

Hogg studied physics at The University of Nottingham, before completing a PhD at The University of Sheffield in Semiconductors. He has over 22 years of post-doctoral experience in industrial and university research, including at NTT Basic Research Laboratories (Japan) and in Professor Arakawa’s Laboratory at the University of Tokyo as an EU-Japan Fellow. He held a research position at Toshiba, Cambridge, and had a key foundry management role at Agilent Technologies, Ipswich, which was, at the time, the highest volume III-V facility in Europe. He has been Professor at the University of Sheffield, where he worked from 2003 to 2015 and is now Professor of Photonics and Head of Electronics and Nanoscale Engineering at the University of Glasgow.

Engineers at ISFOC have racked up more than ten years of experience in operating, optimising and analysing CPV plants. To find out what they have learnt over that time Richard Stevenson quizzes CPV technology manager Maria Martinez and maintenance manager Eduardo Gil.

Q Broadly speaking, how is ISFOC assessing the performance of CPV?

A Maria Martinez (MM). ISFOC is a public R&D company, and our focus is to foster and promote CPV industrialization. With this purpose, when we were founded in 2006, our goal was to carry out electric power-plant

installations with the CPV technologies available in those days. Up to 3 MW was the first idea.

Technologies were selected in a public call for tenders. In the first phase, three different suppliers were installed [at our headquarters] in Puertollano (Ciudad Real) and in a second location 300km away, Almoguera (Guadalajara).

We have 800 kW in Puertollano and 300 kW in Almoguera in operation and connected to the grid since September 2008. Puertollano is our main installation where most of the performance studies are carried out.

For the power plant of Puertollano, one supplier was Concentrix Solar, who became Soitec Solar in 2009, and since October 2016 is owned by Stace Electric. The second is SolFocus and the third Isofotón – for those two, the suppliers are not available, but we don’t know if in the future someone will begin working again with their products.

We have 200 kW of Concentrix – 36 concentrators of 5.5 kW. Each concentrator has its own inverter.

We have 200 kW of SolFocus. Here we have different types of concentrators, different versions, in order to test them. We have two concentrators of 7 kW; another 28 of 6 kW; and additionally, two more of 9 kW of a next-generation product, which were installed in May 2012. Each concentrator has its own inverter.

And then we have Isofotón. Here we have CPV plants and one flat-PV plant mounted on two-axis trackers, with the goal of making some comparison between CPV and flat PV performance. For the CPV plants we have 27 concentrators of 11.1 kW, with three centralized 100 kW inverters.

The first objective of all these installations was to help the suppliers. They had feedback about the qualification of the modules, the characterisation of the CPV plant, and the long-term performance. We were always collaborating with them and giving them our support to improve their products. All made new versions of their products that can be found here, in Puertollano.

We have a lab for the qualification of modules (standard IEC-62108) and trackers (standard IEC-62687). New developers have been always working with us. We can carry out tests to improve the product during the design phase.

We also have in our installations the prototypes of new developers, for instance Isofoton and Semprius. Isofotón installed in 2012 two concentrators of their last generation. Also, we have a prototype, but not connected to the grid, from Semprius. The CPV module of Semprius set a world record efficiency of 33.9 percent in 2012 and at ISFOC the real performance of the module in real operation in the field was assessed.

Q Is your local climate typical for a CPV installation?

A MM. No. We have a good, sunny summer, but during winter we have lots of cloudy days.

During the summer, when we have plenty of hours with high values of direct irradiance, we often observe peak values higher than 1000 watts per square metre. So, for assessing CPV, I think we are a good location, because we have high temperatures and high irradiance values. We also have some sunny and cold days that are very helpful to model CPV technology in best operating conditions – high irradiance and low temperatures.

The DNI in Puertollano is around 2,200 kilowatt-hours per square metre. It’s one of the highest values in Europe, but it is far away from values in South Africa or Australia, where they see 3500 kilowatt-hours per square metre.

Q The role of the compound semiconductor industry is to provide multi-junction cells that operate at high levels of concentration. So far, is it fair to say that your data suggests that the cells are up to this task?

A MM. Yes, although we are not experts in evaluating solar cells in depth, we can indicate that not too many issues, related to solar cells, have been detected so far.

We are members of the IEC committee, and what we see is that there is a lot of effort being carried out to improve the efficiency and performance of CPV cells, keeping always in mind the reliability of the devices.

CPV optics focusing the sunlight onto a CPV cell

A: MM. The first thing that I want to remark is that this module was used for making the installation here in 2007. At the beginning of the project, all the technologies were required to pass some IEC-62108 tests to ensure the reliability of their design, and this technology was failing some of the tests.

In Spain, in those days, a feed-in tariff existed for PV installations, and to obtain those benefits it was mandatory to connect our plants before September 2008, since an important income for ISFOC comes from selling this electricity. Therefore, we decided to go ahead with the installation of this version of the product, although we knew it was failing in some lab testing.

On the one hand, from an R&D point of view, this was a great opportunity to verify if the failures detected in the lab were going to be reproduced in the field. On the other hand, we had a contract with the manufacturer, to maintain our income. If the failures were reproduced, affecting the performance, they would replace some of the concentrators. Finally, failures were repeated in the field. In 2012, they replaced the 18 kW with a new- generation product that was IEC-62108 certified.

The first issue occurred in the first years. It was the gasification of some of the materials inside the module, that were deposited over the optics surface. The effect is like some scattering of the light, reducing the energy that reaches the cells.

There was also some damage to the secondary optics caused by the concentrated sunlight, some kind of failure in the reflective coating.

The most important result that we obtained from this experience is that the IEC-62108 standard is working. It was possible to detect in the lab, with tests, some of the failures occurring in the field.

But some other failures were not possible to detect, so further work is needed in the standardization committee to modify the tests if possible. Failures related to long-term exposure to direct or concentrated sunlight are

not so easy to reproduce.

Q: Do you think that when designed with skill and care, modules can be robust, showing minimal degradation?

A: MM. Yes. We have some technologies that have been operating for more than ten years. Up to now, everything is working at the same level as it was in the beginning.

It’s also important to say that our installations are prototypes. The next products were even better than the ones we have here.

Q: Based on your data, what have we learnt about the reliability of tracker designs?

A: Eduardo Gil (EG). I would like to remark that our trackers are based on preliminary designs. At the time, the CPV community focused its efforts on developing CPV modules to be as efficient and reliable as possible. When we started operating and maintaining our CPV power plants, we started to be aware of the importance of other components.

We learnt that the identification of all key components responsible for the vast majority of unavailability is essential to reduce unplanned intervention, increasing the reliability of the trackers. However, if reliability and maintainability weren’t taken into account during the early stages of the design, when the cost of making any change is cheaper, the cost of increasing the reliability during the operation time would be unaffordable.

Q: Do you see any concerns relating to reliability when moving to higher concentrations, such as focusing light by 2000 suns rather than 500 suns?

A: MM. We are not experts in cells. Going to a higher concentration means that more heat dissipation in the module and the cell is needed. Most modules have passive cooling. And perhaps higher concentration will require active

cooling, which it is not desirable because it would be more complex and expensive during installation and O&M tasks.

We have systems here with small cells that are working up to 1000 suns. But going to higher concentration, in my view, may require a move to dense CPV receivers with solar dishes or parabolic mirrors, including active cooling for heat dissipation – like Solar Systems, Raygen, in Australia.

I know that one way to reduce the cost of a concentrator is to increase concentration without increasing the cost of the rest of the elements. But I think that perhaps 2,000 suns is too high at present.

A CPV receiver illuminated through a multi-phase reflective optic

Q: To me, it is the parts of the system that I have given little thought to that are to blame for the most failures. These are control systems and firmware. Why have they been so problematic? And can these weaknesses be addressed?

A: EG. Not all software and firmware is problematic. That only occurred with one of our partners who decided to design their own inverter, due to the fact that there wasn’t in the market any specific inverter for CPV technology.

We also suffered from hardware issues. That inverter included the control system in the same box. It had caused several problems, because of the heat generated inside.

Thanks to our data analysis and support, they improved the software and were aware of the heat dissipation problems.

Some years later, some inverter manufacturers adapted their design for CPV technology. This partner decided to use commercial inverters in their system, avoiding the problems of the combination of inverter and the controller of

the tracking system.

Q: A significant proportion of CPV downtime is also due to issues associated with encoders and limit switches. What’s the role of these components, and can they be improved?

A: EG. A tracker usually has two encoders: one for the elevation axis, and one for the horizontal axis. Basically, the encoder is a counter. It sends the position of the tracker to the control board.

Regarding the limit switch, it is used to prevent the tracker from reaching a forbidden position during operation. It’s a normally closed contact, but when it is pressed, the contact opens and stops the current.

We now have more than ten years of experience in the operation and maintenance of tracking systems. We have detected many of these components located in an improper place. Most of the time, the encoder is in a place where, for example, water can get inside; if it were better located, it would work properly. It’s not really a problem with the component; it’s a problem with the design of the tracker.

Q: Now that the most likely causes of failure for a CPV system have been identified, what figures should be possible for uptime and annual degradation?

A: EG. Up to now, we don’t have enough records to answer this question. In our opinion, the degradation of mechanical parts is always a controversial topic and depends on not only the maintenance strategy deployed but also on the operational environment where the CPV is installed. High winds, extreme temperatures, heavy rains, etc., will play an important role.

MM. And if we talk about degradation of the CPV technology itself, the CPV modules, we can say that this is one of our fundamental analyses. We are continuously analysing the performance of the CPV plants but filtering out all the data related to maintenance and operation incidences, which means analysing the performance of the CPV technology only. We compare the energy of production with the DNI accumulated for the different years of operation. What we have up until now – and what we hope will continue in the future – is that the level of degradation is less than one percent per year. It’s in the same level as flat PV.

Q: Is there a role for preventive maintenance in the operation of a CPV plant?

A: EG. Of course there is a role for preventive maintenance in the operation of CPV plants. Preventive maintenance is essential for boosting the market confidence of this technology. Many people believe that maintenance is an extra cost, however, from our point of view, it’s an investment. During the first years of operation of our CPV power plants, we evaluated and adapted all the operation and maintenance protocols for CPV technology, which allowed us not only to increase reliability of our CPV power plants, but also to reduce drastically the maintenance costs, increasing the uptime of the systems installed at our facilities.

The main idea is that we pay for maintenance to gain reliability and availability of our CPV plant. Optimised maintenance strategies increase production revenue, and that means more income for the investor.

Q: You have found that operation incidences would be lower if more support were given by suppliers. But some suppliers are no longer in business. That must be a concern for efforts to rejuvenate this industry, as investors in CPV will want to be supported by system makers that will be in this industry for many years to come?

A: MM. Economic issues have really strangled the photovoltaic sector.

Manufacturers of CPV were trying to develop a different product, like some special PV technology, so for them it was even more difficult to obtain funds from banks or investors. Without investment, you cannot make any improvement to the technology. A lot of companies were pushed to close their business, because of this crisis.

I think, and hope, that new CPV developers will not suffer from this issue. The story of Concentrix, Soitec and Stace Electric shows that if you have a good a product, someone will have confidence in it.

I hope that in the near future we will have again big partners in this industry.

Q: Compared to the figures quoted about a decade ago, is the levelised-cost-of-energy coming down, due to a greater understanding of reliability issues?

A: EG. The levelised-cost-of-energy is coming down due to two main reasons. On the one hand, the CPV installation cost has dropped significantly from 2009 to 2018 – this fact strongly affects the levelised-cost-of-energy.

On the other hand, our maintenance strategy has allowed us to increase reliability. In other words, it has allowed us to reduce the maintenance cost, so the levelised-cost-of-energy also comes down because of this cost reduction.

Moreover, it is important to remark that year-after-year, the three-junction cells are beating the efficiency record. This also helps to reduce the levelised-cost-of-energy.

Q: Do you see any signs for a possible re-birth of the CPV industry?

A: MM. Yes, I think so. Inside the community, what we see is that again there are new developers, university researchers and small companies fighting to demonstrate that their product has a place in the electricity generation market.

A sample of active companies nowadays: BSQ Solar, Spain; Raygen, solar dishes and central tower receivers, Australia; Morgan Solar, Canada; MagPower, Portugal; and don’t forget about Stace Electric, Canada, who currently owns the technology of Concentrix Solar.

Moreover, we must name some projects that are funded by public entities, such as CPV4all and CPV Match, demonstrating that there are some interesting developments in CPV.

Finally, it must be said that there are new CPV concepts under development that could enlarge the market of the technology – like hybrid CPV-thermal systems, which use an active cooling of the solar cells to warm up fluids – or BICPV – building integration CPV – that are being explored by the CPV community.

One of the CPV plants located at ISFOC headquarters

Satellites could be powered by incredibly efficient modules featuring five-junction micro-cells and tiny glass lenses

BY MATTHEW LUMB FROM GEORGE WASHINGTON UNIVERSITY

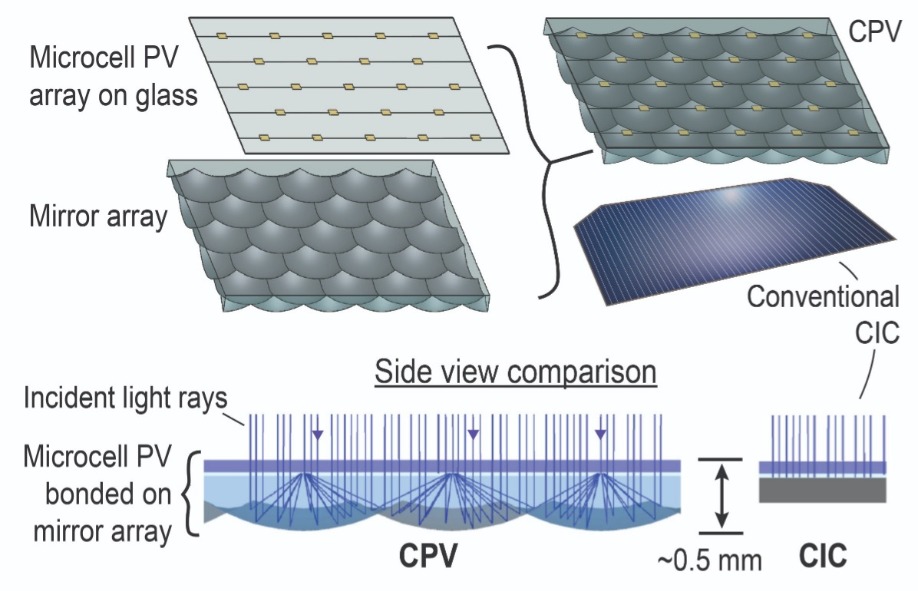

By far the most efficient class of technology for converting sunlight into electrical power is the high concentration photovoltaic (HCPV). Modules that are based on this technology use low cost lenses or mirrors to focus sunlight onto multi-junction cells with three or four junctions, to realise conversion efficiencies at the cell level that are nearing 50 percent. Note that the focusing of sunlight by factors of typically 500 to 1,000 is critical to increasing the bang-per-buck of this technology: it spawns a hike in conversion efficiency, as well as slashing cell costs, due to a dramatic reduction in the amount of compound semiconductor material required to deliver a given output.

The commercial success of HCPV has been thwarted by several factors, limiting this field to a handful of companies. Arguably the most damaging of thorns has been the rampant success of low-cost, large-area solar cell technologies, particularly crystalline silicon. But there are other issues, such as the requirement for precise two-axis tracking, which adds cost and complexity to an installation, while limiting packing density due to shadowing. Another impediment is that it is impossible to focus diffuse light with conventional optics, so utility-scale CPV is restricted to desert-like locations, where the diffuse sunlight fraction is small.

One glimmer of hope is that conventional, large-area silicon solar panels are now beginning to push firmly against their fundamental efficiency limits. So, if a large boost in HCPV efficiency came along at low cost, and were combined with the remarkably high energy yield available from two-axis tracking of the sun, this solar technology could be highly competitive once again.

Further cause for optimism is the emergence of myriad niche applications where the key requirement is maximising the number of watts per square meter, rather than the cost per watt. The former metric is the priority in remote and space-confined applications, such as bicycle and car-charging stations; in temporary DC microgrids, such as those used for disaster response; and in the application we will focus on in this article – space power.

Cell considerations

During the last decade, many CPV companies have closed up shop. But the majority of cell suppliers have not suffered the same fate, thanks to a healthy market for III-V multi-junction solar cells in space. Here they are the established industry leader, with numerous multi-junction solar cells on the market. Success stems from a different set of priorities: cost-per-watt is a secondary consideration, and topping the list is the specific power, judged in watts-per-kilogram, and the volumetric power density, evaluated in terms of watts-per-cubic-metre.

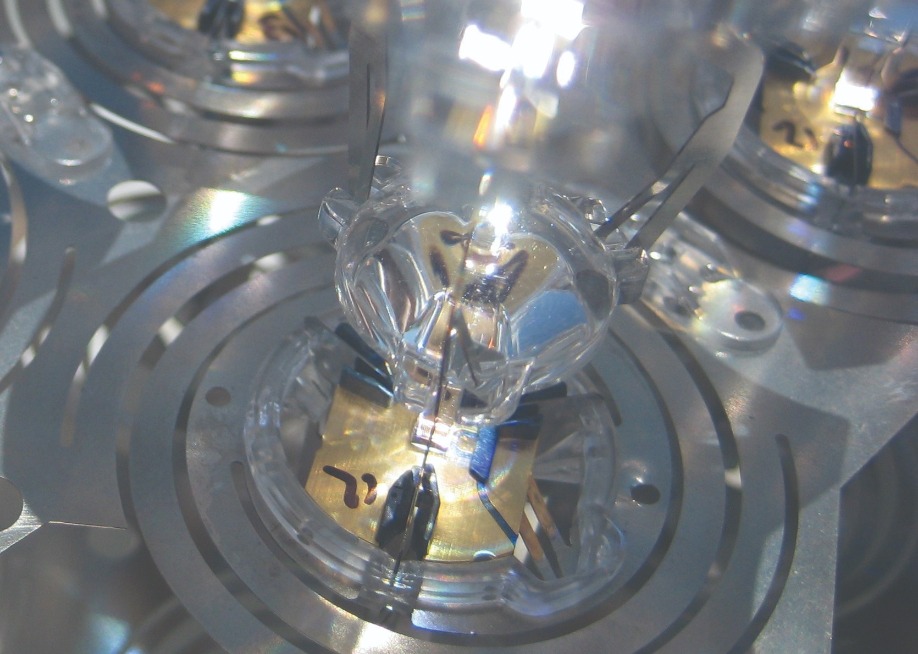

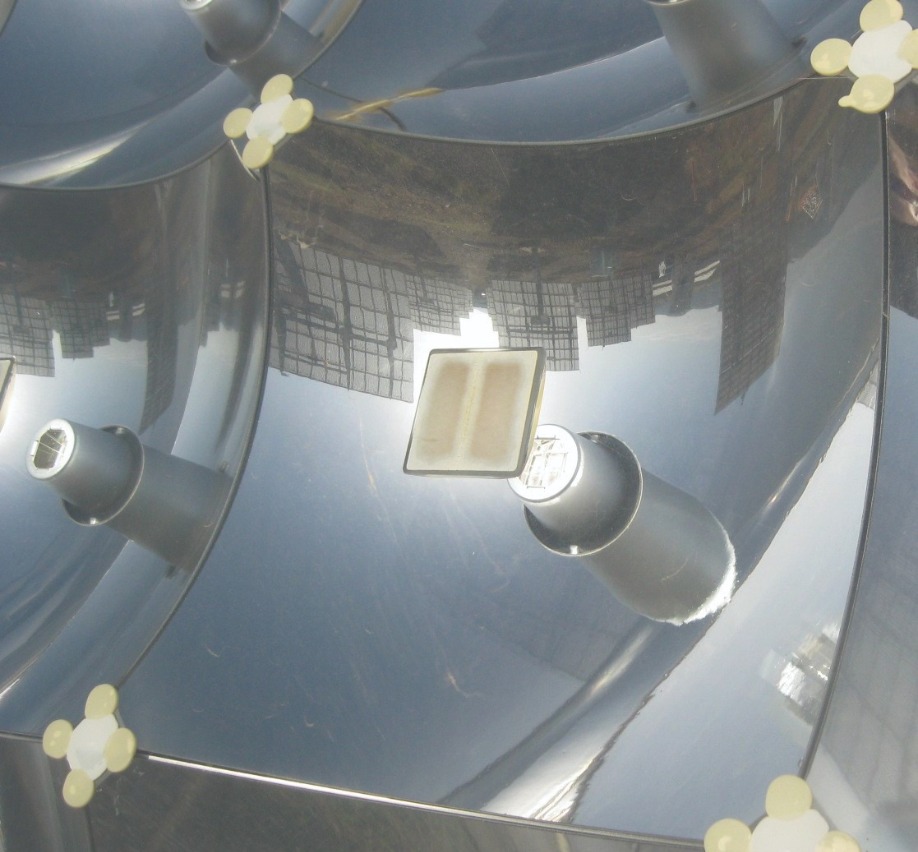

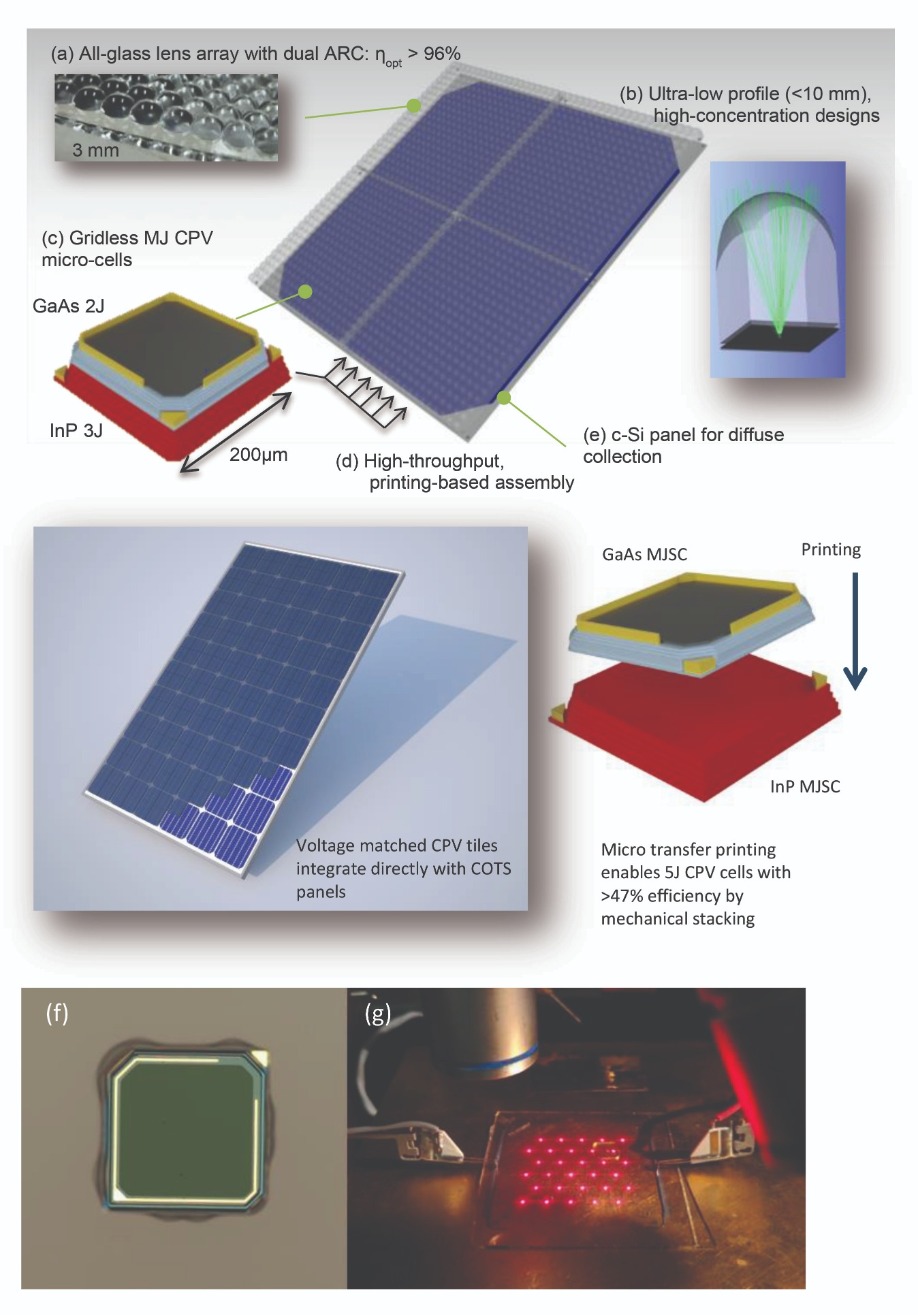

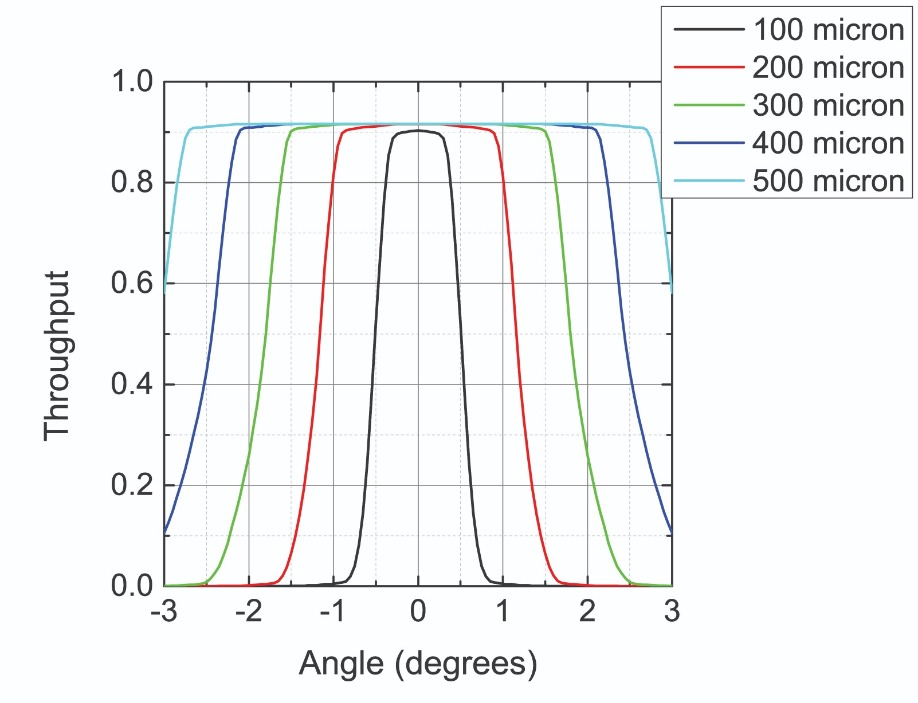

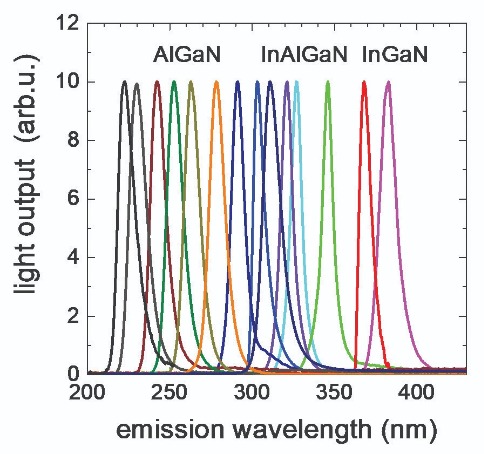

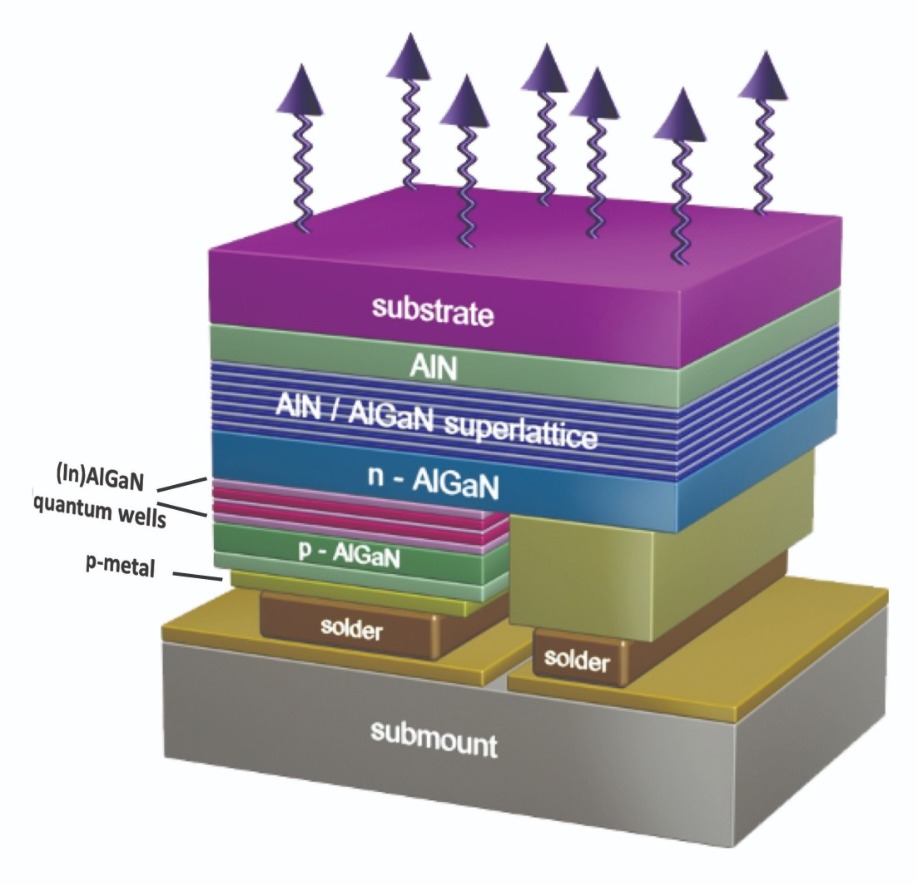

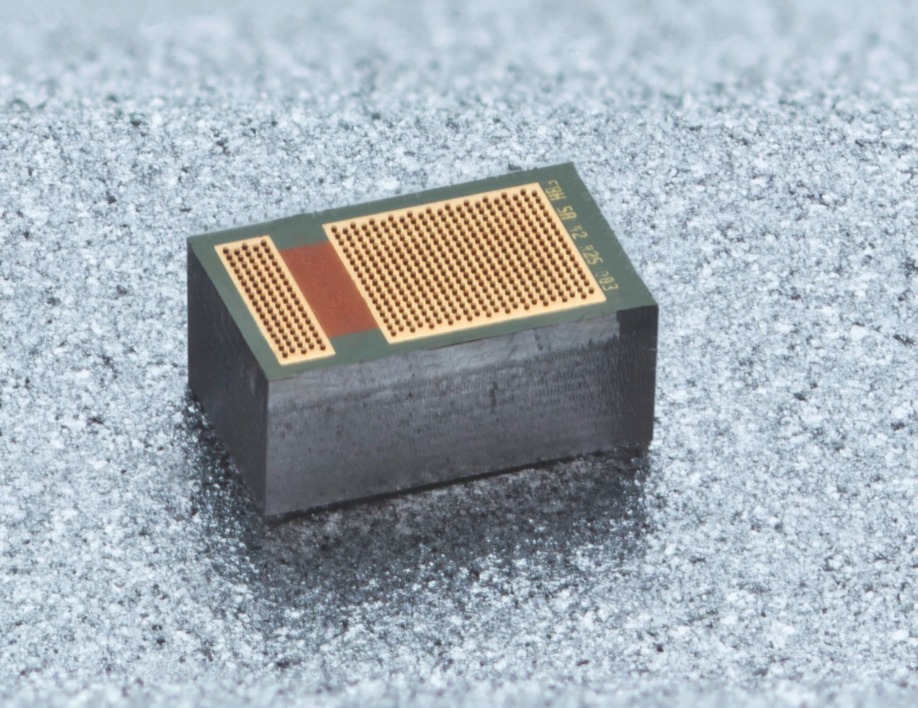

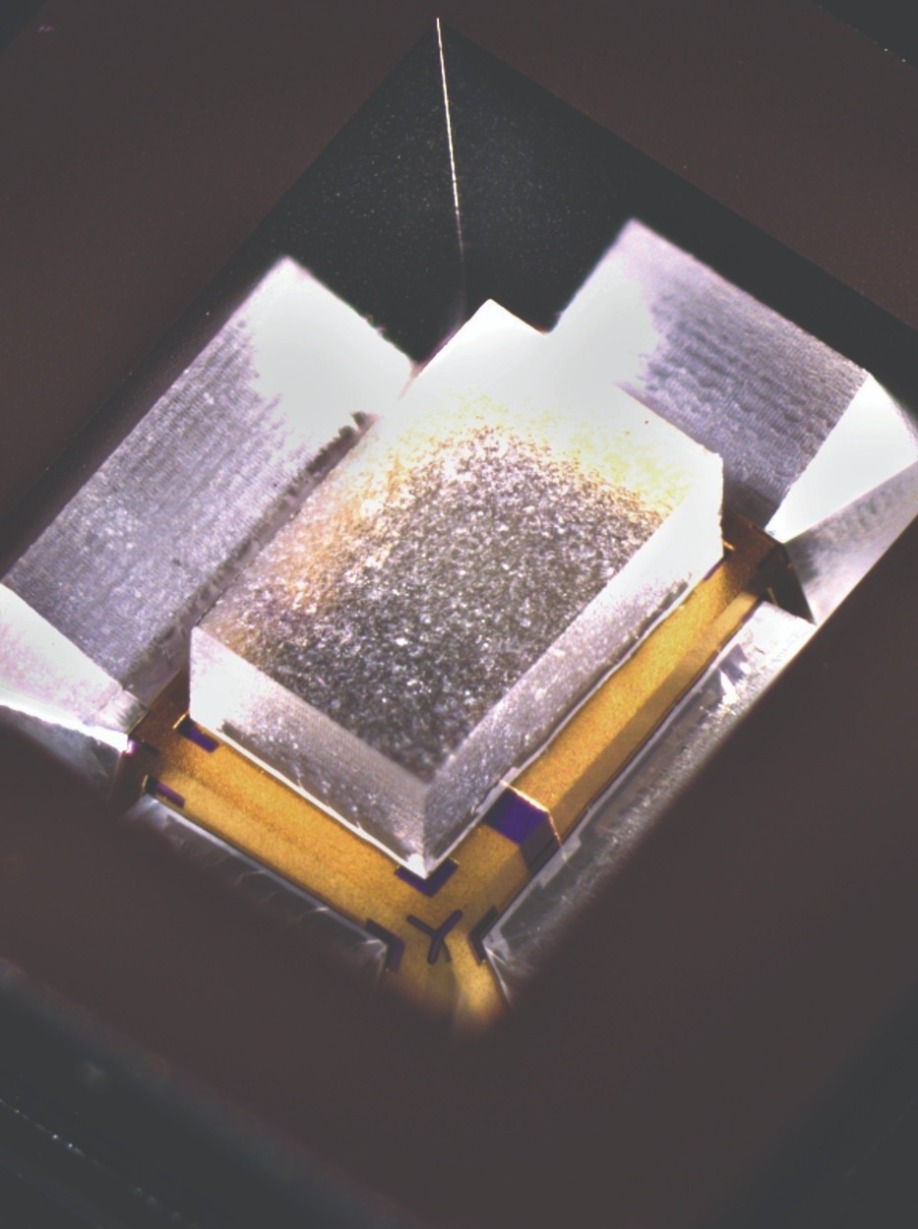

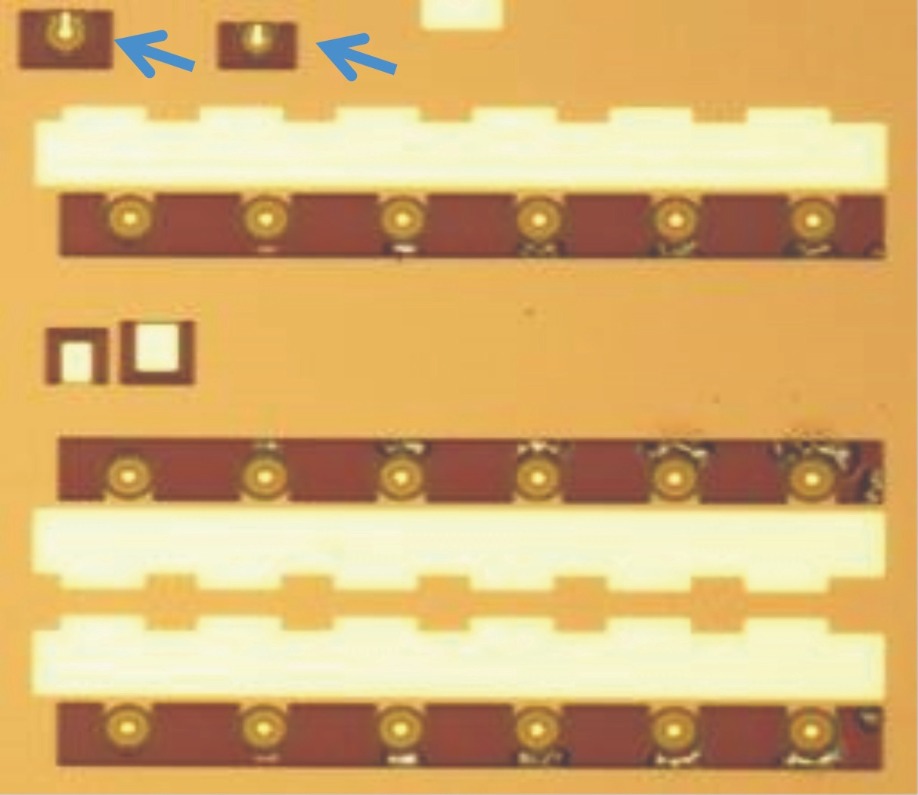

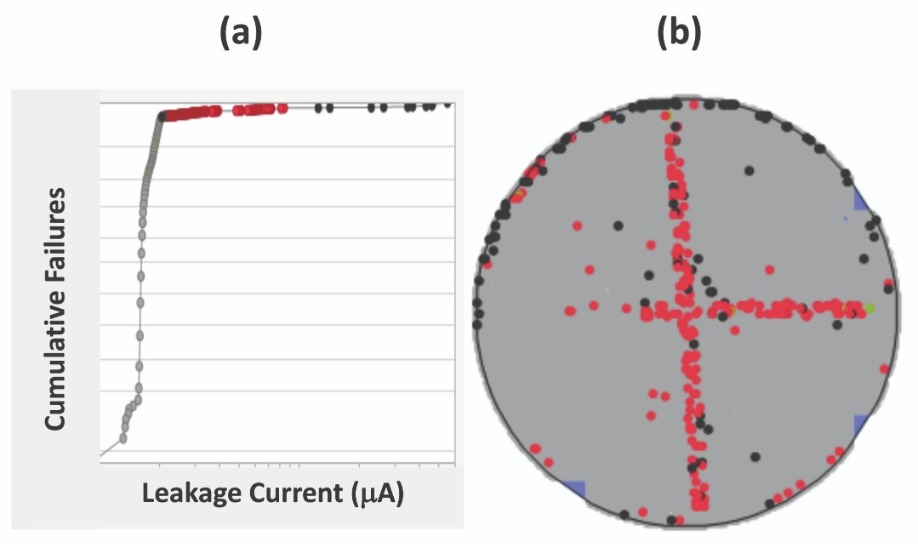

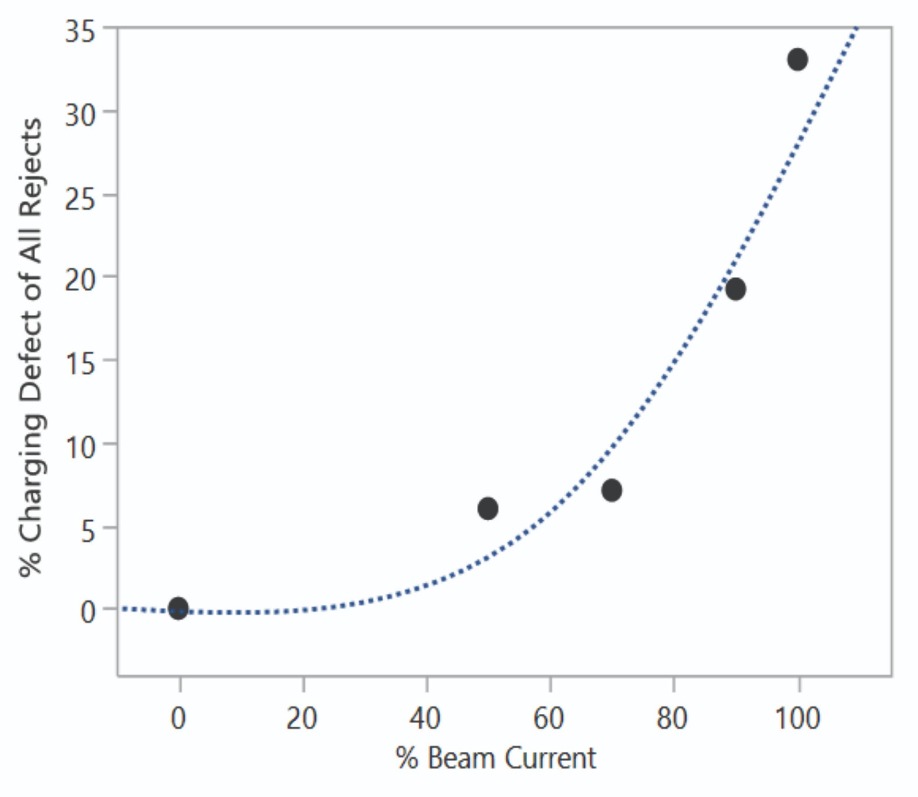

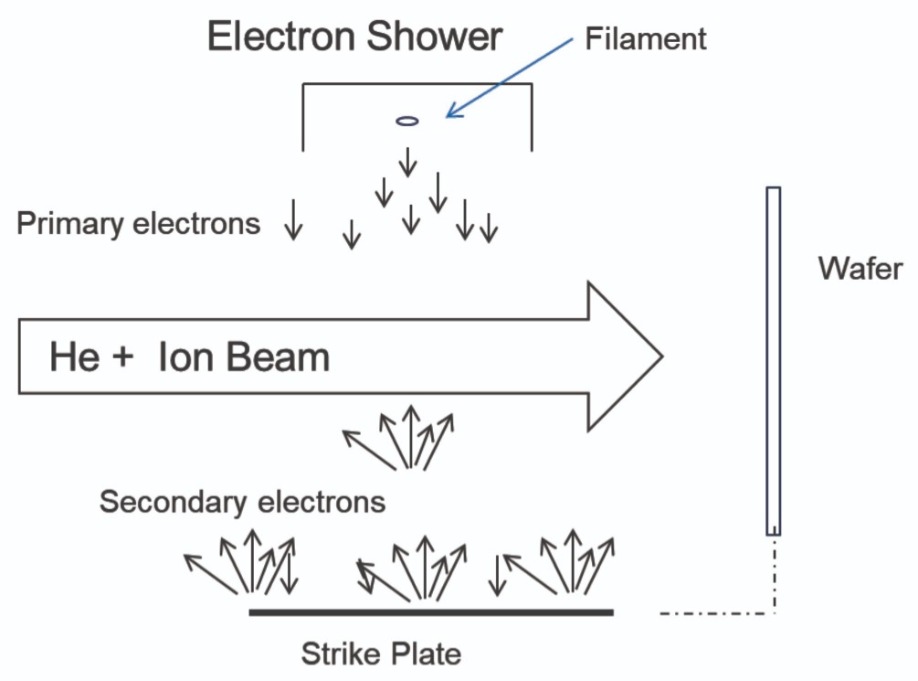

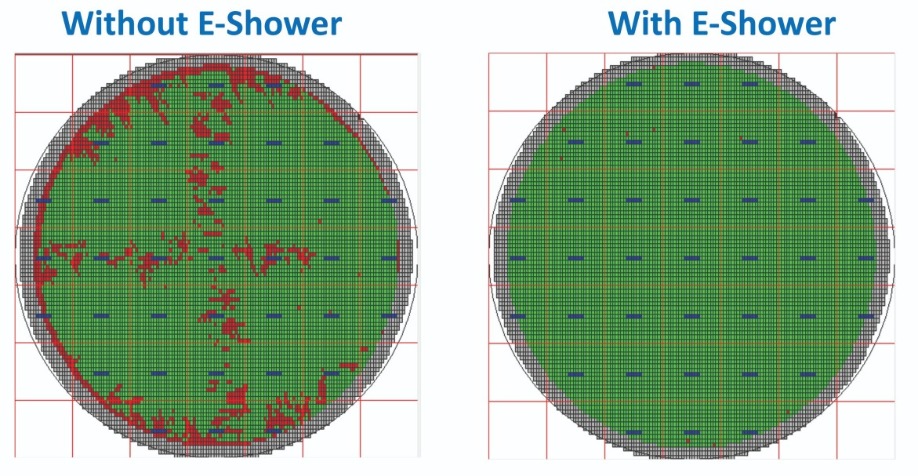

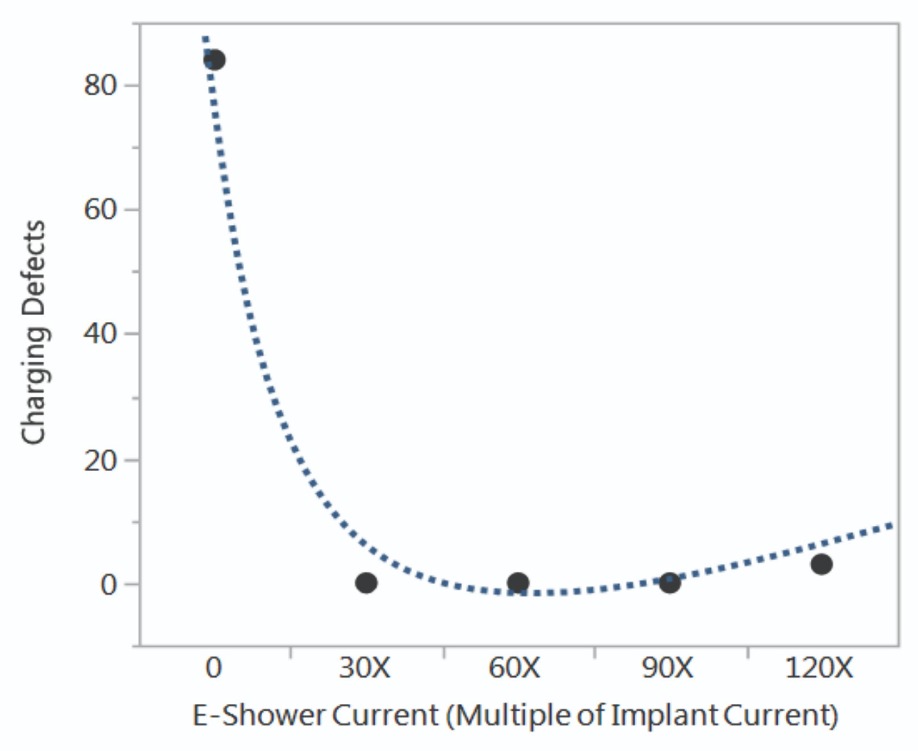

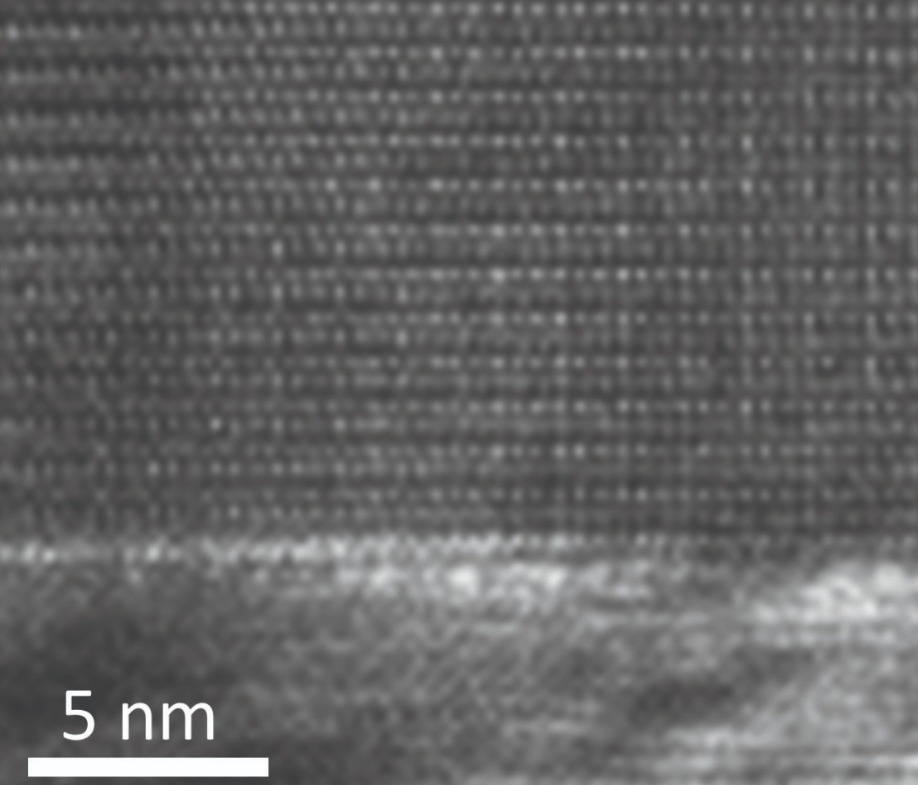

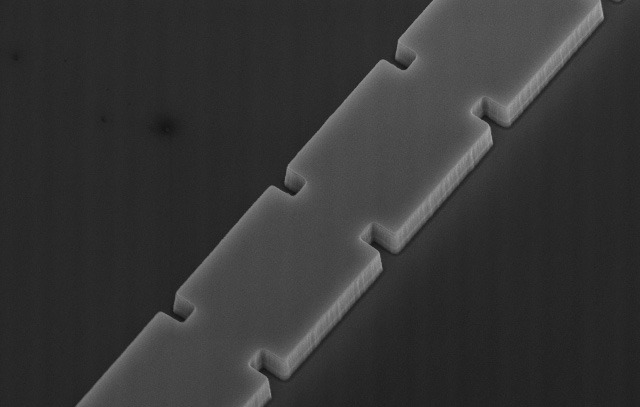

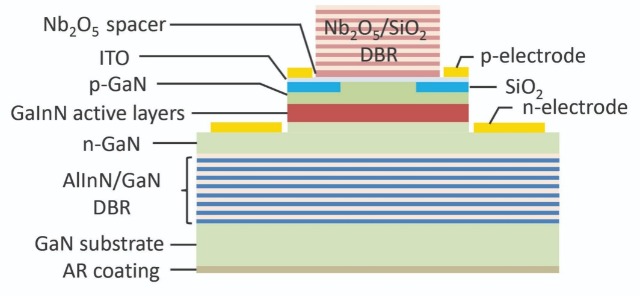

Figure 1. (a)-(e) The main features of the micro CPV design, which has been developed by a team that is led by researchers at George Washington University. Modules incorporating state of the art CPV microcells, all-glass optics and diffuse collection using off-the-shelf crystalline silicon solar panels. (f) A GaAs-based dual-junction microcell transfer printed on to a glass substrate. (g) A hexagonal array of dual-junction microcells under forward bias, operating as LEDs.

The need for a high specific power reflects the very high launch cost for putting anything in space. Regardless of what it is, it costs in the region of $10,000 per kilogram. So, to drive down launch costs, solar cell suppliers try to produce the lightest weight cells possible.

The other key consideration is the volume of the payload. To minimise this, extremely creative and hi-tech photovoltaic panel deployment systems are employed on satellites. They feature low profile modules and large-area, III-V multi-junction solar cells with industry leading performance.

Devices that work well on earth may not do so in space, due to the far higher levels of radiation that degrade material quality and reduce efficiency. To minimise this over the lifetime of the cell, suppliers encapsulate their devices in tens to hundreds of microns of cover glass. This coating shields the semiconductor layers from radiation, but adds significant weight to the final product.

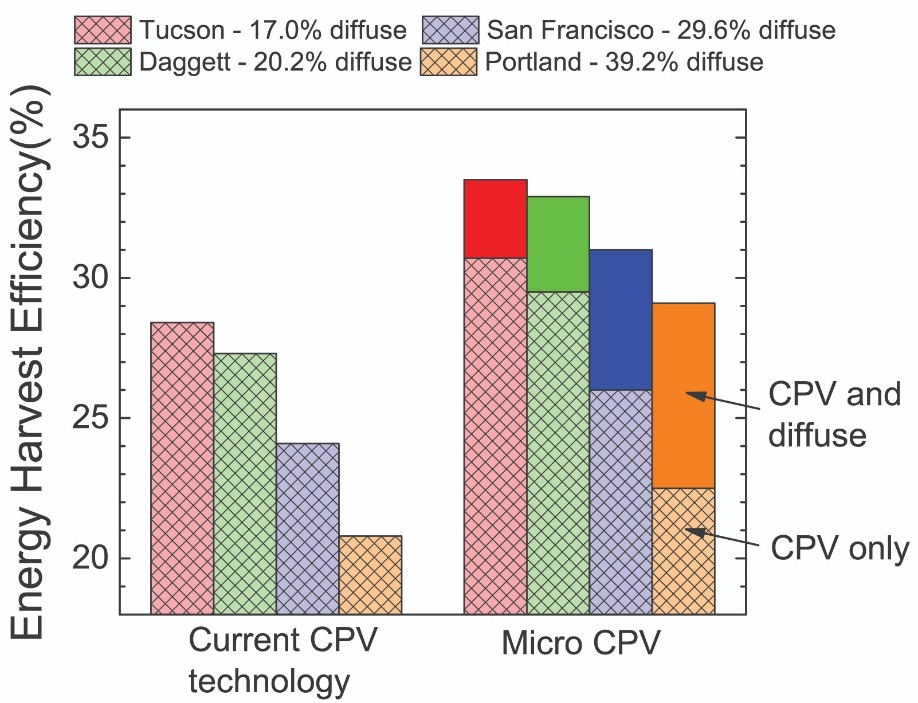

Figure 2. Predicted DC global energy harvest efficiency (annual kWh production / annual global resource on a two-axis tracker) in locations with different diffuse contents for conventional HCPV and a micro-CPV array.

CPV in space?

There have been several notable, successful experiments based on taking CPV panels into space. These efforts, aimed at exploiting the high efficiency of the technology to increase specific power, have focused on low concentration demonstrations that have failed to gain a strong foothold. But this time it could be different, thanks to the advent of a new type of CPV technology – micro CPV. Its timing could not be much better, given that multi-junction cells operating at one sun are reaching practical limits for efficiency and specific power; and the advent of reusable rockets, coupled with large increases in space traffic, could drive down launch costs.

Helping to develop a new generation of CPV technology for space is the US Department of Energy’s Advanced Research Projects Agency-Energy (ARPA-E). Through the programme MOSAIC – Micro-scale Optimized Solar-cell Arrays with Integrated Concentration – it is funding 11 teams with a total of $24 million.

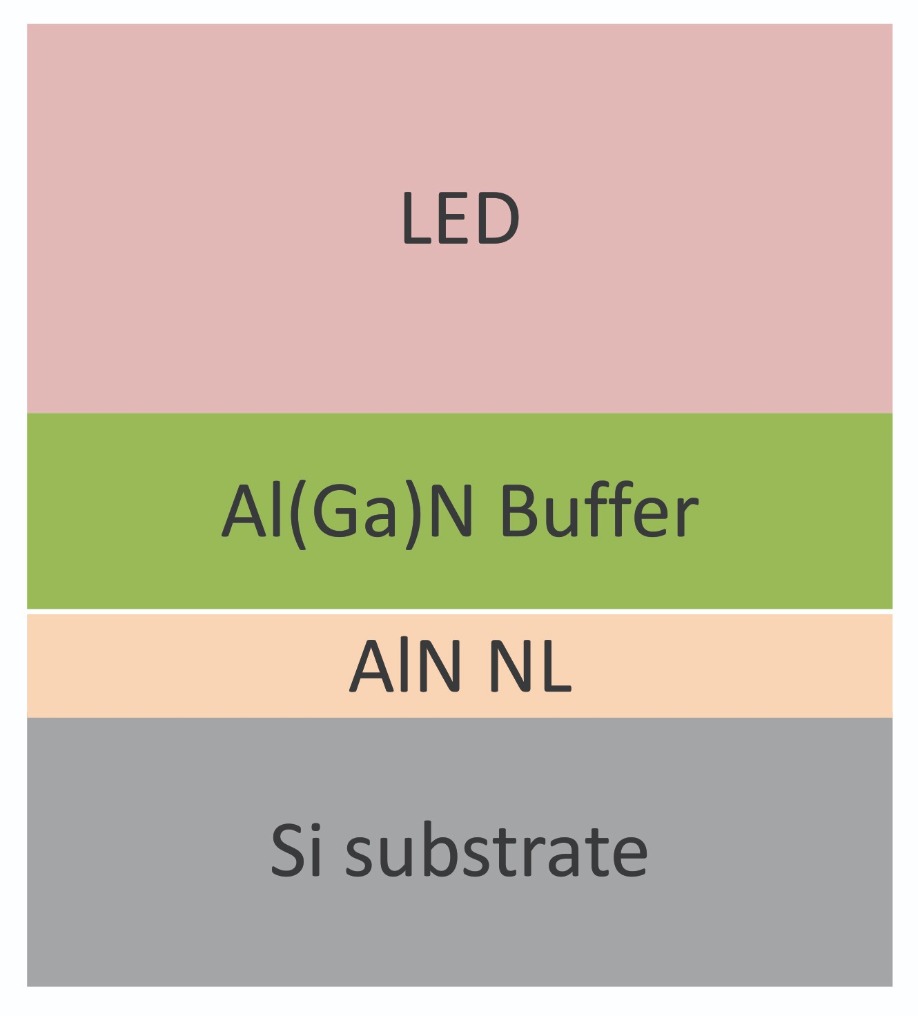

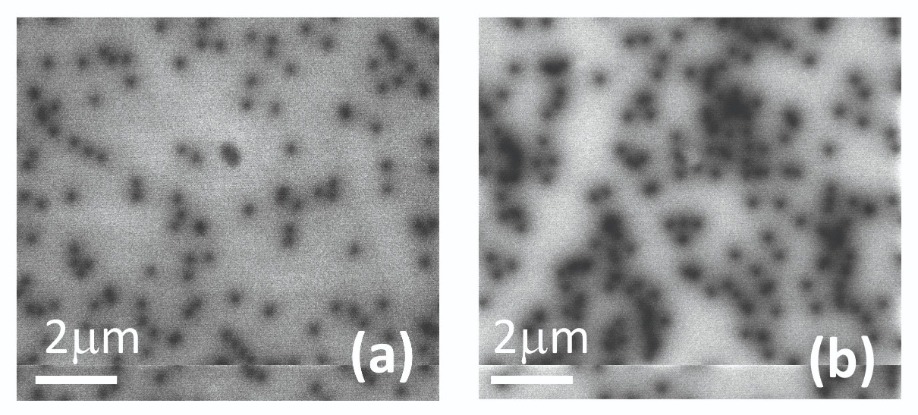

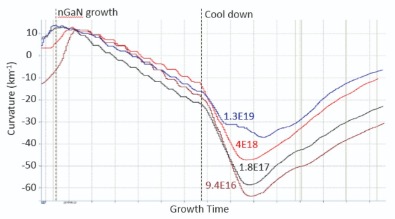

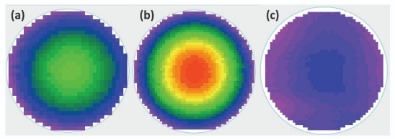

The efforts that ARPA-E are supporting include those by our team at George Washington University, working in partnership with researchers at the US Naval Research Laboratory, Veeco, Northwestern University, MIT and X-Celeprint. Together, our collaboration is aiming to address some of the main obstacles facing conventional HCPV by marrying ground-breaking, ultra-high-performance five-junction cells with all-glass lens arrays and a glass backplane (see Figure 1 for an overview). Our glass lenses feature a novel, bifacial anti-reflection coating that provides an extremely high optical efficiency while concentrating sunlight by a factor of approximately 500.

One of the great strengths of our modules is that they can capture diffuse light, thanks to the incorporation of a bifacial, crystalline silicon solar panel. Attaching this to the CPV module injects a significant boost to the overall power output, especially in locations where a large fraction of the total solar resource arrives as diffuse illumination (see Figure 2).

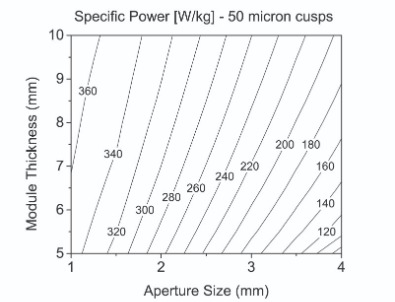

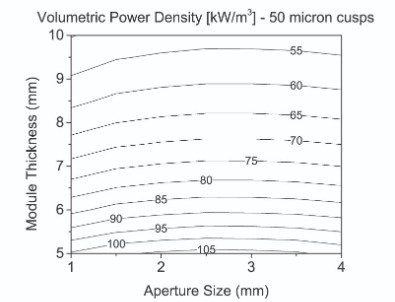

Figure 3. Specific power and volumetric power density for different lens designs for the five-junction CPV cell developed by the team led by researchers at George Washington University.

Our micro CPV module is also able to excel in efficiency. The apertures for our CPV cells are just 170 μm by 170 μm, so the devices are small enough to avoid the use of metal grid fingers when efficiently extracting current from the cell. Instead, a single metal contact is employed at the edge of the aperture, eliminating shadowing loss. Another benefit of using microscale cells is that they simplify thermal management. Thanks to this, cells can operate at lower temperatures, thereby churning out power at higher efficiencies.

We assemble our microcells with a micro-transfer printing process, a technology commercialized for PV by former CPV company and team partner Semprius. Note that this is also the core technology of our industry partner, X-Celeprint: it applies micro-transfer printing to a range of micro-optoelectronic applications.

Micro-transfer printing allows precise, parallel assembly of microscale devices that are removed from their native substrate with a wet etch procedure. In addition, we use micro transfer printing to heterogeneously integrate dual-junction, GaAs-based solar cells with triple-junction InP-based solar cells. The five-junction cells that result – featuring high quality, lattice-matched materials – capture a broad range of the solar spectrum. Do this at low cost, and it can be disruptive to conventional PV technology.

Our CPV module is well-suited for use in space. Its merits include: a very high radiation tolerance, thanks to shielding by the glass lens array; a reduced arcing risk between cells, due to their large separation; and a low profile module, enabled by focal lengths of just a few millimetres. Those dimensions allow units to be drop-in replacements for conventional panels, and be compatible with existing deployment techniques.

In missions to deep space, it’s actually an advantage to operate multi-junction cells at high concentration. That’s because this negates many of the difficulties associated with low-temperature, low-intensity environments. These issues, which include complications arising from hetero-barriers and trap states, are encountered on missions to parts of the solar system much farther from the sun.

Yet another strength of our CPV modules is that they have the potential to be far cheaper than large-area III-V solar cells. This benefit will become increasingly important in the future, due to decreasing launch costs.

Figure 4. Optical throughput versus incident angle for glass lenses with a

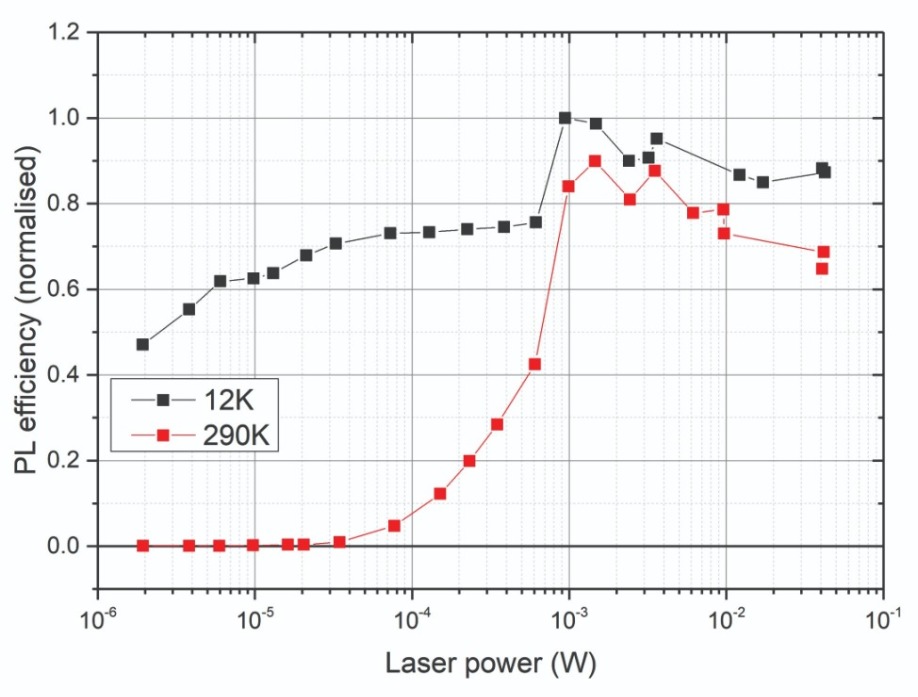

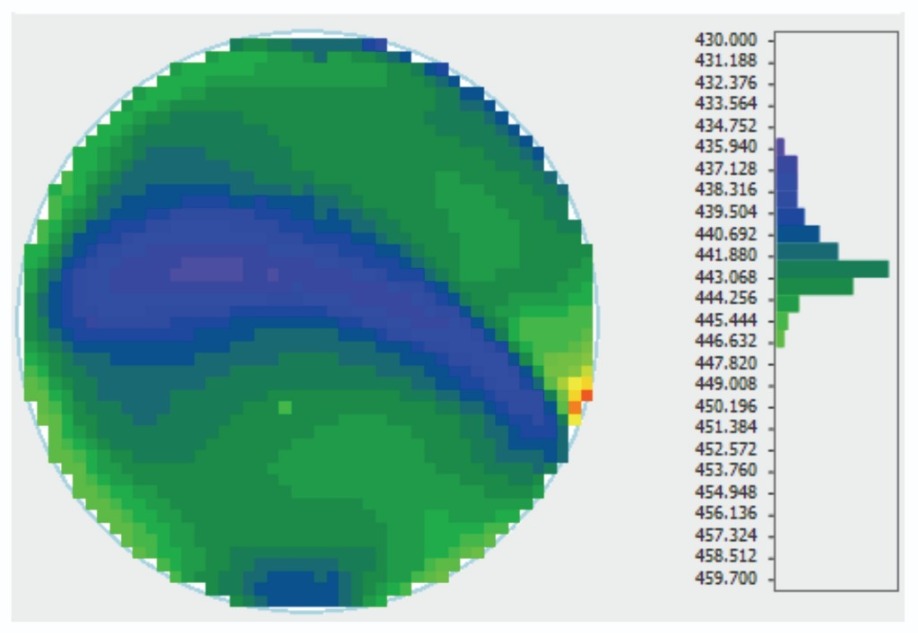

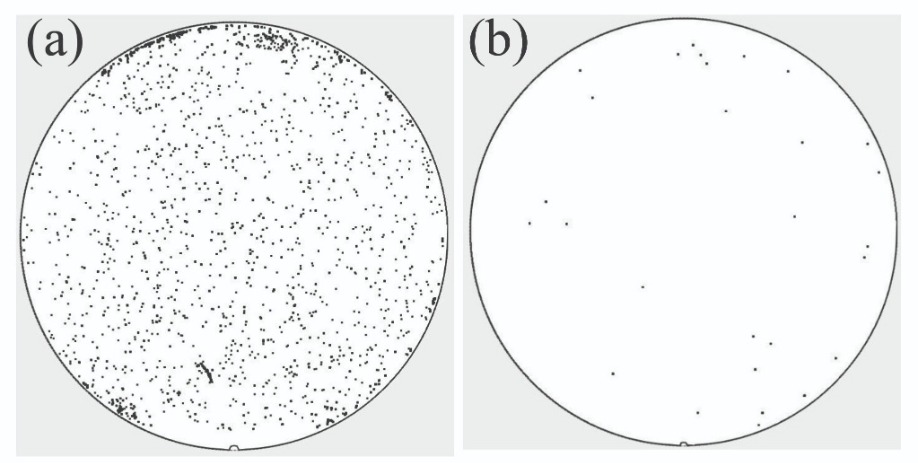

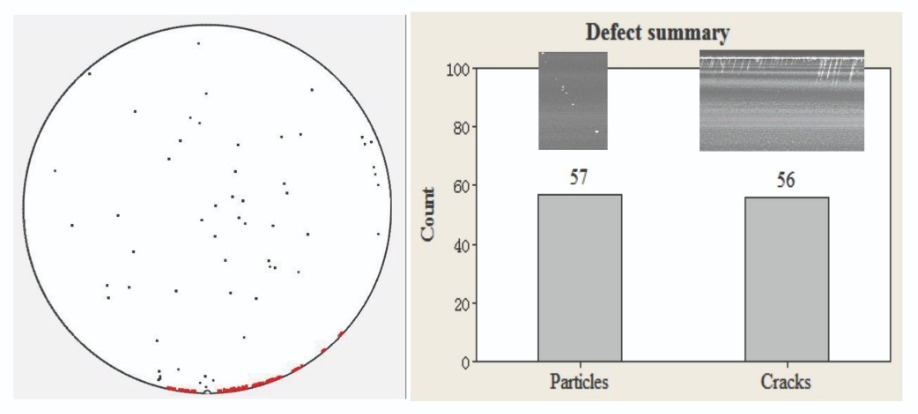

Sweet spots